A COMPLETE GUIDE TO LOW COST TELEVISION DISPLAY OF ALPHA-NUMERIC AND GRAPHICS DATA FOR MICROPROCESSOR SYSTEMS, COMPUTER HOBBYISTS, HAM RITY, TV TITLING, WORD PROCESSING AND VIDEO GAMES.

# TV Typewriter Cookbook

by Don Lancaster

# SYNERGETICS SP PRESS

3860 West First Street, Thatcher, AZ 85552 USA (928) 428-4073 http://www.tinaja.com Copyright © 2010 by Synergetics Press Thatcher, Arizona 95552

THIRD EDITION FIRST PRINTING-2010

All rights reserved. Reproduction or use, without express permission of editorial or pictorial content, in any manner, is prohibited. No patent liability is assumed with respect to the use of the information contained herein. While every precaution has been taken in the preperation of this book, the publisher assumes no responsibility for errors or omissions. Neither is any liability assumed for damages resulting from the use of the information contained herein.

International Standard Book Number: 1-882193-13-4

Created in the United States of America.

# Preface

This book shows you how to put your own words and pictures on ordinary ty sets. It's also a book on cheap things that can be connected to a microprocessor to get it to do genuinely useful tasks. If you are a computer hobbyist with a home-brew lashup, a serious professional data processor concerned with low-cost small machine systems, a video games freak, or a ham working with rtty, you will find in depth information on tv typewriter technology, which today represents the only truly low-cost (\$30 to \$150) microcomputer and small-systems display interface. If you are a software specialist, we will be showing you the hardware that makes your software work, giving you the depth of background you will need for effective and efficient small-systems coding. If you are teaching microprocessors, you will find this book useful as a primary or supplemental text on the high school through university levels. If you are into video recording, cable tv, or studio broadcasting, you will find techniques here for low-cost titling and annotation of existing program material, as well as the means for video art synthesis. And, if you are an electronics technician, herein lies the answers on the standard ASCII code; serial transmission formats; keyboards and encoders; Teletype, cassette, and modem techniques; along with many of the integrated circuits and systems concepts that back them up.

We start in Chapter 1 with some basics—what a tv typewriter is and what are its uses, configurations, and operating principles. After this, we take a quick look at the fundamentals of television raster scanning, followed in turn by the standard computer codes and their formats. A collection of essential terms involved with tvt's and microcomputer interface then follows.

Chapter 2 is a catalog of integrated circuits you will find useful in tvt and interface work. It is organized in much the same way as the similar device chapter of the *TTL Cookbook*, also published by Howard W. Sams & Co., Inc.

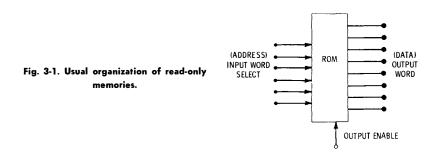

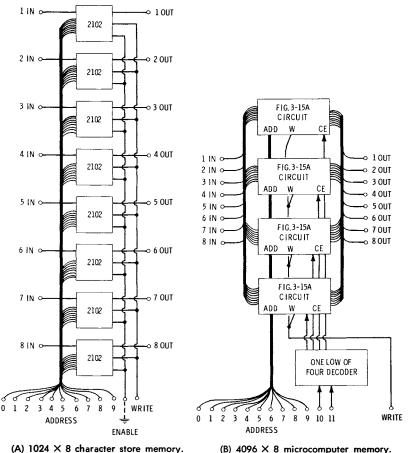

Memory is the topic of the next chapter. We consider three basic types: you-program PROMs, including a seven-segment calculator interface and a Selectric converter; factory-programmed ROMs, including particularly the dot-matrix character generator; and readwrite or RAM technology that lets you selectively store and retrieve information. The 2102-style devices and their improved offspring are emphasized because of their ultralow cost, extreme simplicity of use, and microprocessor compatibility.

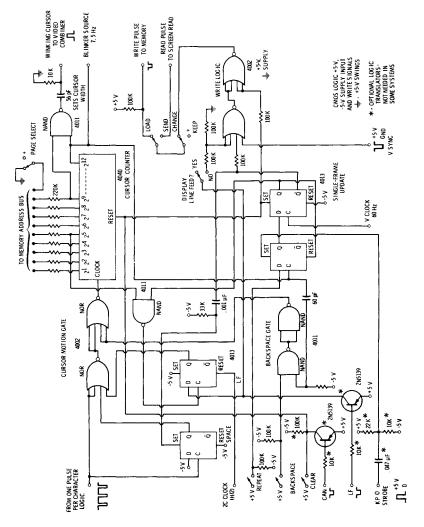

Basic concepts of tvt system design appear in Chapter 4, including such things as timing-chain design and line-lock and EIA sync techniques. Cursor and update circuitry, which is usually the hardest-todesign part of a stand-alone tvt, is covered in Chapter 5. Cursor techniques range from the traditional count and compare and the ultrasimple McFadden system, to dedicated "super front panel" tvt's that work directly with microcomputers. Update systems include both frame-rate and direct memory access (DMA) systems.

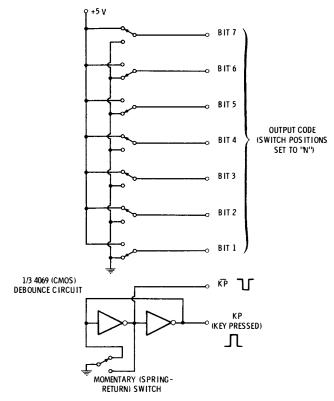

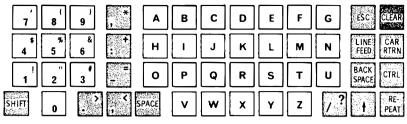

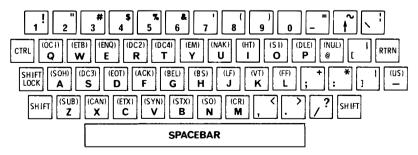

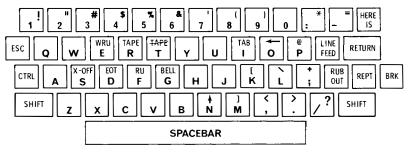

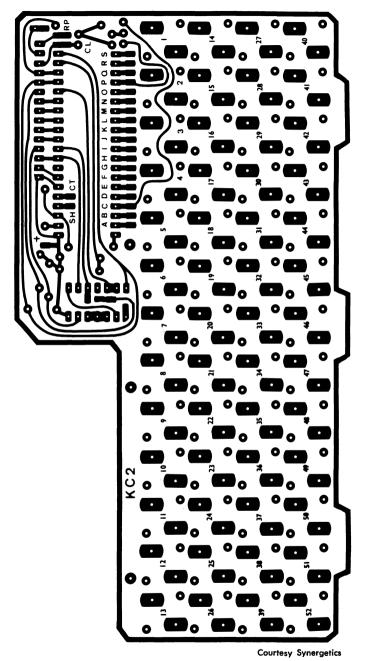

Keyboards and encoders follow in Chapter 6, with a number of basic encoding techniques, key arrangements, and circuits shown.

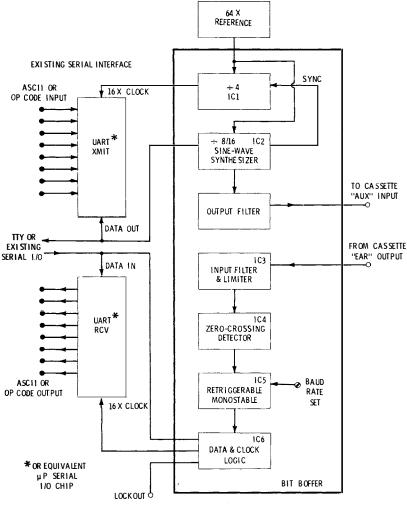

An extensive review of serial interface centered around the UART, or universal asynchronous receiver transmitter, is presented in Chapter 7. Here we also look at the bit boffer software-independent, speed-tolerant cassette storage system, along with Teletype and standard interfaces and various types of modems.

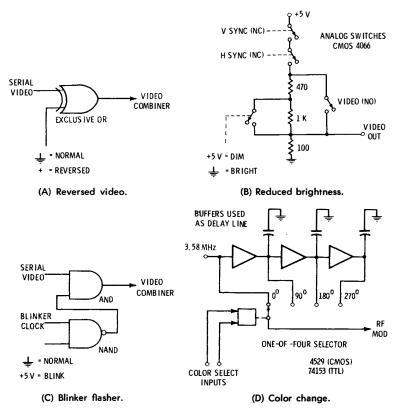

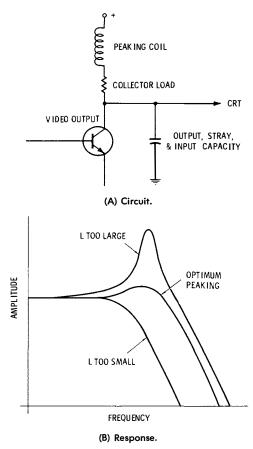

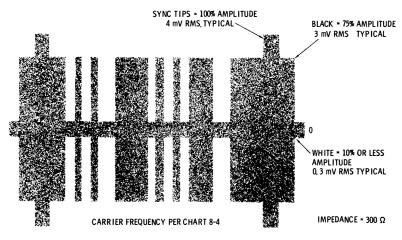

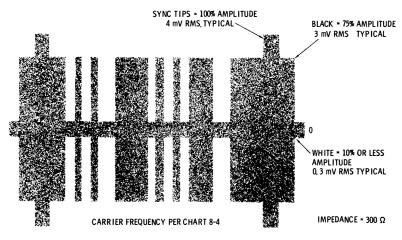

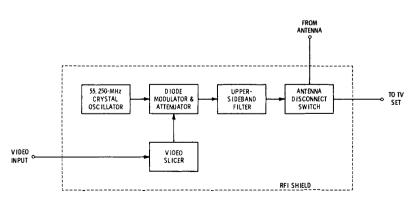

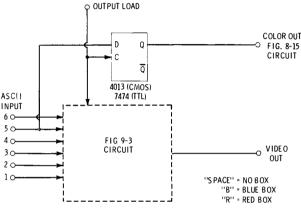

The care and feeding of the tv set are next in Chapter 8, which shows us both the rf and direct-video methods, along with several ways of extending video bandwidth for long line-length displays. We end the chapter by looking at color subcarrier techniques—simple ways of adding one or more colors to your system for video games or art synthesis, or for other applications where you want to use color for added emphasis or value.

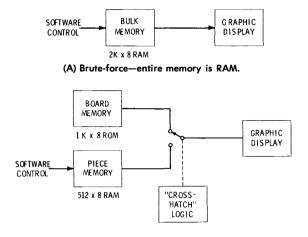

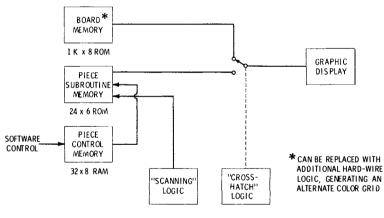

Our last chapter is on hard copy (printed records) and color graphics. The full gamut of hard copy is covered, from computer Teletypes, Baudot Teletypes, and economical Selectric office typewriter conversions, to ink squirters and special paper systems that include the electrosensitive, thermal, impact, and photographic systems. Our color graphics section shows you both ultracheap ways of converting an ordinary tvt into a limited-performance graphics mode and into a sophisticated  $96 \times 96$  color matrix system that includes "chess" and "pong" interchangeable software. Finally, we take a quick look at where you can go from here—what is needed now in the way of further tvt-related development in which you can play an important part.

DON LANCASTER

This book is dedicated to an amplifier with nothing to amplify.

# Contents

#### CHAPTER 1

#### **CHAPTER 2**

| INTEGRATED CIRCUITS FOR TVT USE                             | 26 |  |  |  |  |  |  |  |

|-------------------------------------------------------------|----|--|--|--|--|--|--|--|

| Baud-Rate Generators—Character Generators—Keyboard Encoders |    |  |  |  |  |  |  |  |

| -Line Drivers and Receivers-Programmable Read-Only Memories |    |  |  |  |  |  |  |  |

| -Random-Access Memories-Serial Interface UARTs              |    |  |  |  |  |  |  |  |

#### **CHAPTER 3**

#### **CHAPTER 4**

#### **CHAPTER 5**

#### **CHAPTER 6**

#### CHAPTER 7

#### **CHAPTER 8**

#### CHAPTER 9

#### CHAPTER 1

# **Some Basics**

A tvt, or *tv typewriter*, is any low-cost way of displaying lots of words, numbers, or graphics on an ordinary tv set. The single most important use for a tvt is that of an input/output device for a microprocessor or microcomputer, but the concept of using a low-cost, mass-produced display to present locally generated and used information is incredibly broad. It is so broad that tvt techniques represent a totally new communications media—a decentralized media that is based on the fast and easy transfer of information rather than the difficult and energy-intensive moving of physical objects, particularly cars and people.

So, what can we do with a \$30 to \$150 machine that puts words and pictures on a tv set? Some of the uses we know of today include:

- \* Computer terminals

- \* Video games

- \* Microprocessor "super front panels"

- \* Video titling

- \* Deaf communications

- \* Calculator readouts

- \* Advertising displays

- \* Touch typing learning aids

- \* Teaching machines

- \* Electronic notebooks

- \* Remote message centers

- \* Cable tv response units

- \* Mailing list generators

- \* Word processing and editing systems

- \* Color graphics displays

- \* Political polling

- \* Ham rtty

- \* Phototypesetting

- \* News, weather, and stock displays

- \* Community direct-information access systems

There are several overlapping ways we can classify the different types of tvt that are available:

A *stand-alone* tvt does just that. It can interface with any source of information, with or without a microprocessor, and contains its own cursor, update, storage, and modification circuitry.

A *dedicated* tvt is usually intimately associated with a microprocessor or other devices that make the tvt a component part of a larger system. Typical dedicated applications include tvt's used as microprocessor *super front panels*, on which the tvt can display every memory location in the entire computer system on a page-at-atime basis; word-processing applications in which extensive editing, rearranging, or format changes are needed; and "pong" and chessstyle games in which move computation is needed.

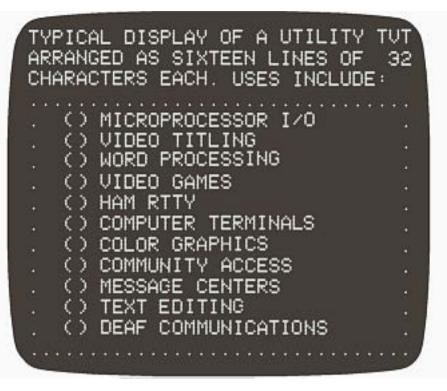

A *utility* tvt usually displays 16 lines of 32 characters at a time, most often in an uppercase-only  $5 \times 7$  dot-matrix character format. This type of tvt has very simple timing requirements, a minimum memory cost, and is cheap to build, interface, and use. Often a second *page* of memory is internally provided to increase the total display to 1024 characters on a selected basis.

A premium tvt can display more information and uses fancier character presentations that include lowercase and that have better character definition. These presentations can display as many as 4000 characters simultaneously, and a quarter of a million or more resolvable elements in graphic displays. Premium tvt's almost always need a modified tv set that has additional display bandwidth. They are usually associated with larger memories, faster components, higher cost, and more critical timing.

Since a television set has no internal way to store information for more than a tiny fraction of a second, a memory, often called a *refresh memory*, is needed and must somehow be associated with the tvt. A tvt with *dedicated internal memory* has its own internal storage available only for its own use.

A shared internal memory tvt has its own memory but makes it available to other circuits on a DMA, or *direct memory access*, basis. This is handy for games and calculator displays.

An *external memory* tvt simply borrows the information it needs from a microcomputer, microprocessor, or other system memory any time a display is needed. An *input/output*, or i/o, tvt has ways of both accepting and returning information. If we have a cassette storage interface, a modem, or a hard copy (printer) associated with the tvt, or if we have the ability to retransmit the tvt screen or to sense a portion of it with a *light pen*, we have an i/o tvt.

A *read only*, or RO, tvt can only accept and display information without electronically returning any of it. Typical examples are a microprocessor memory readout and a game graphics display.

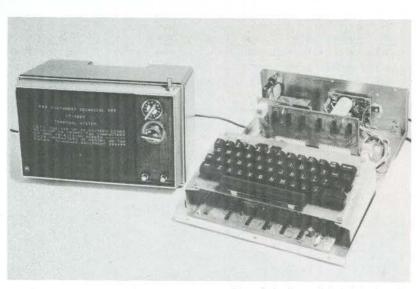

Courtesy Radio-Electronics Fig. 1-1. The tvt-1 using TTL and shift-register memory.

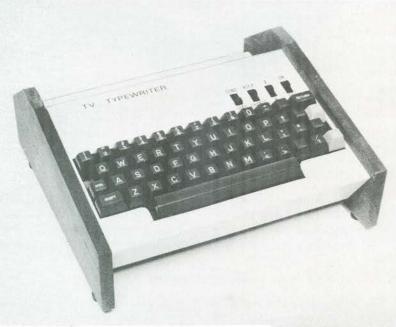

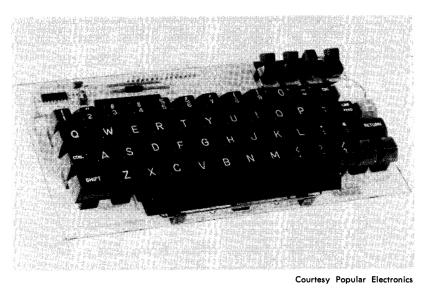

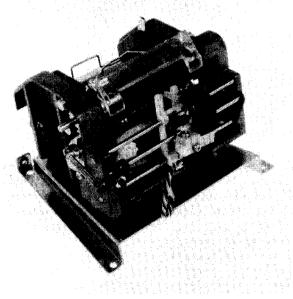

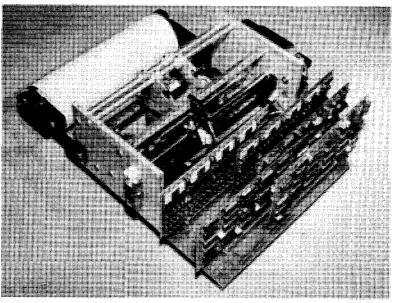

Figs. 1-1 through 1-3 show some typical early stand-alone tvt's representing three generations of design. Sources of tvt's include Polymorphic Systems, Processor Technology, and Southwest Technical Products. Fig. 1-4 shows the typical display of a  $16 \times 32$  utility tvt.

#### ORGANIZATION

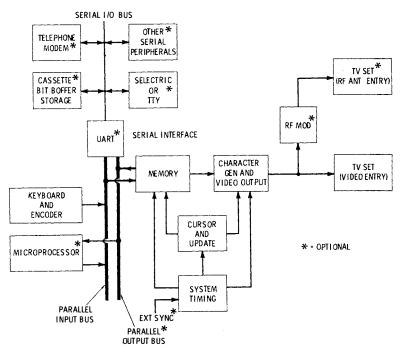

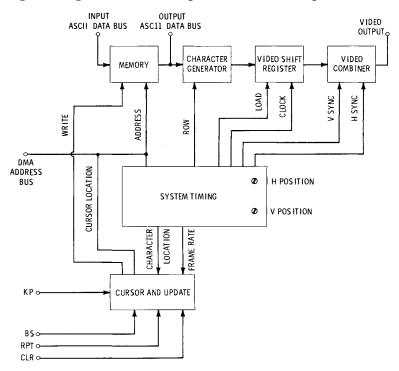

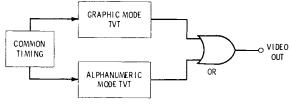

The arrangement of our tvt system is very much a dynamic and changing process, owing to the recent (at this writing) dramatic cuts in memory components and microprocessor circuits. Fig. 1-5 shows one possible block diagram of a tvt.

Courtesy Southwest Technical Products Co. Fig. 1-2. The tvt-2 system.

Courtesy Synergetics

Fig. 1-3. The tvt-3 uses CMOS and RAMs; it is 8-bit microprocessor DMA compatible.

Fig. 1-4. Typical page display of utility tvt.

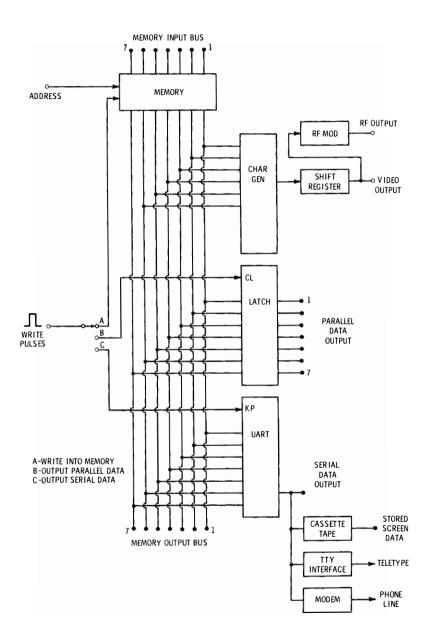

A memory is an essential part of a tvt. The memory has to store the characters for us, delivering them to the tv as needed to generate the desired display. As we have seen, this memory can be a dedicated internal memory, an internal memory accessible from the outside, or an external microprocessor or minicomputer memory. The memory is often arranged as 1024 words of 8 bits each, with one memory word associated with each displayed character or a close grouping of graphic display dots. The 2102-style MOS random-access memory or one of its improved offspring is often a good choice for tvt memory. We will be looking at these devices briefly in the next chapter and will take a detailed look at them in Chapter 3.

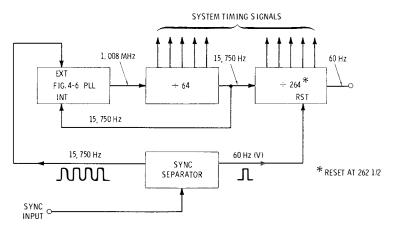

Our tvt has to have some system timing that converts and presents information in such a way that a television set is able to use it. The system timing is usually faster than can be handled by early microprocessors and is often done by a half dozen or so dedicated integrated circuits, which are often stock TTL or CMOS chips. System timing also provides for line locking to eliminate weaving or "seasick" displays, and optionally allows us to lock onto an existing program for titling annotation, or adding the scores to a graphic

Fig. 1-5. Block diagram of typical tvt system.

game display. Chapter 4 covers many of our system timing problems and solutions.

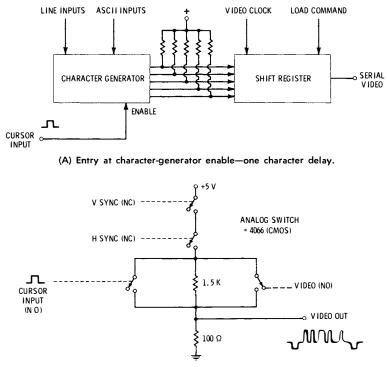

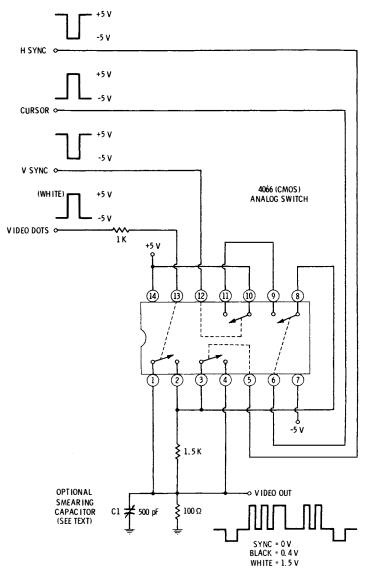

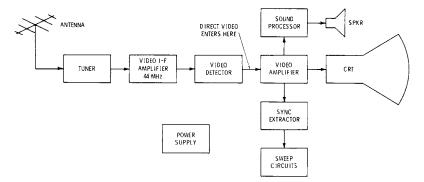

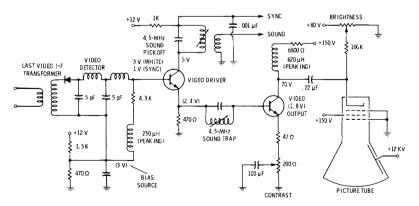

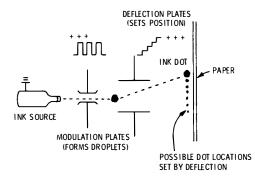

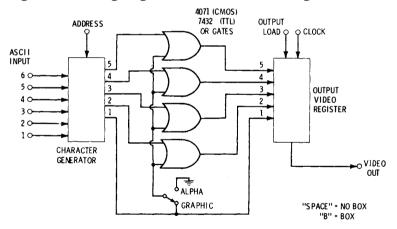

The character-generator and video-output block converts the six to eight bits worth of character stored in the memory into an expanded group of dots that we see as a character on the screen. We have the options of using *direct video* that is wired into the tv set or using an rf modulator that gives us clip-on antenna entry to an unmodified tv. Details on these particular circuits appear in Chapters 3 and 8.

A cursor and update circuit takes care of adding new material to the memory and the display. The cursor itself is usually a blinking box, underline, or overline that shows the user where a new character is to go. Cursor updating can be done with a frame-rate system that takes 1/30 or 1/60 of a second to enter a single character, or with direct memory access (DMA) that lets us fill the entire screen in 1/60 of a second or so. Direct memory access is obviously much faster but is usually more complex and not directly compatible with the speeds associated with cassette data recorders, modems, and hard-copy devices. We have the option of building the cursor into the tvt or doing it externally under microcomputer control. Related to the cursor circuits is an optional *screen-read* circuit through which the formatted, corrected, and otherwise edited screen display can be retransmitted or sent along to another system in *parallel* or *serial* form. This is particularly useful for assembling blocks of data for cassette recording. Chapter 5 covers cursor techniques in depth.

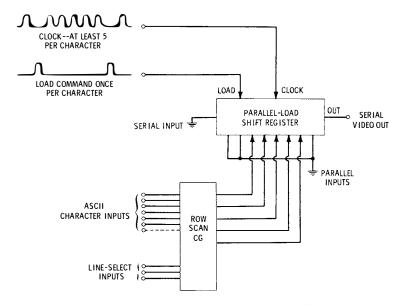

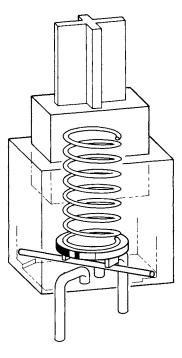

Normally, tvt's are set up to accept their input words in *parallel* form (all the bits at once). Parallel form is cheaper and faster, and is convenient to use with keyboards and microprocessor data buses. Details on keyboards and encoders appear in Chapter 6.

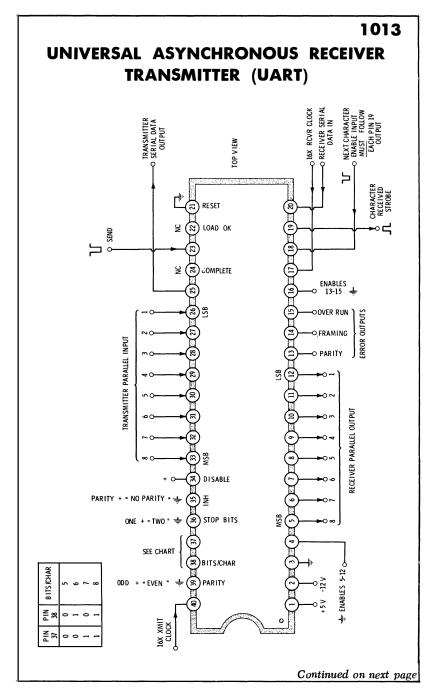

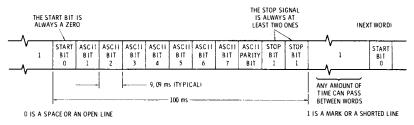

Another convenient input form is *serial* data, in which the bits march down a single line in sequential order at a specified rate. Since tvt's are basically parallel devices, they must be converted to and from serial form with a suitable *serial interface*. A special, low-cost integrated circuit called a *universal asynchronous receiver transmitter* (UART) usually does the conversion for us. This lets us input or output tvt information to a cassette data recorder, a telephone *modem*, a Teletype, a remote keyboard, or another communications channel. Chapter 7 covers these serial interface techniques in detail.

Our final concern is the tv itself. While a clip-on rf entry at the antenna of a stock set is ideal from a convenience standpoint, this approach both restricts the length of character line and needs FCC approval. The alternative is *direct video* entry, which requires set modification and can prove a problem on hot-chassis style tv sets. Chapter 8 shows what we need to know for the care and feeding of a tv set, along with the modifications we can make for direct video, extended response, and multiple color displays.

Two add-on output options for a tvt system are hard-copy (printed records) and color graphic displays. These take a slightly different type of system timing and are covered in the final chapter.

### SOME TV FUNDAMENTALS

The main purpose of a tvt is to convert stored, compactly coded characters located in a memory, into a repetitive form that a tv set can understand and use.

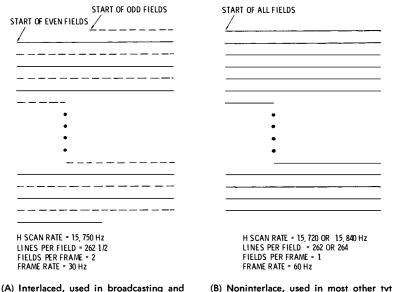

A television set is a *raster scan* device. It puts a dot of light on its screen and moves the dot around rapidly to generate a composite picture. The dot is moved in an orderly manner called a *scan*, starting the upper left-hand corner and going rapidly to the right and slowly downward. Two types of raster scan are the *interlaced* and *noninterlaced* scans shown in Fig. 1-6.

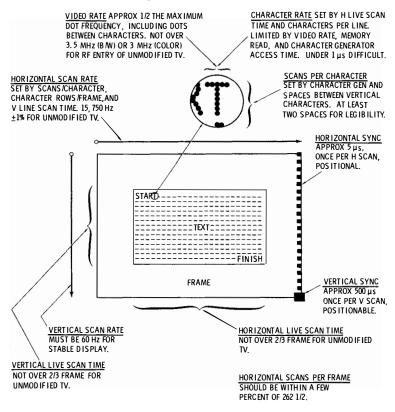

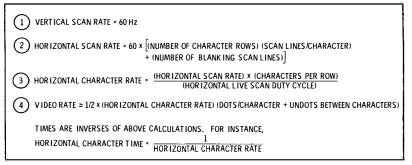

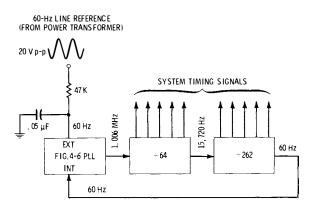

An interlaced system is normally used with tv broadcasts. The horizontal scan rate is 15,750 Hz for black and white and 15,735 Hz

for color. Two trips, or *fields*, are made down the screen for one composite *frame* or single picture. One trip starts at the upper left; the second in the upper center, overlapping or interlacing the two fields into a single frame. There are  $262\frac{1}{2}$  horizontal lines per field and a total of 512 lines per frame. The field rate is 60 Hz, and the frame rate is 30 Hz. This interlace system is normally used to minimize flicker and blur, particularly when associated with fast screen motions.

tvt titlina.

(B) Noninterlace, used in most other tvt applications.

#### Fig. 1-6. Television raster scan.

Interlace is rarely needed for tvt use. The only exceptions are in video titling and other applications in which you are going to *superimpose* a message on top of an existing interlaced program. Instead of interlace, we use a noninterlaced scan as shown in Fig. 1-6B. Often we use either 262 or 264 horizontal lines per scan. We hold the frame rate (which is also the field rate) to *exactly* 60 Hz, so the horizontal scan rate changes to 15,720 Hz or 15,840 Hz. The reason the frame rate *must* be held to 60 Hz is that the poor shielding and excess hum in many television sets will cause a weaving or otherwise seasick display as a result of being slightly off frequency and slowly slipping power line cycles. Often our tvt circuitry will *lock* itself to the power line, an existing EIA-standard video program, or a crystal.

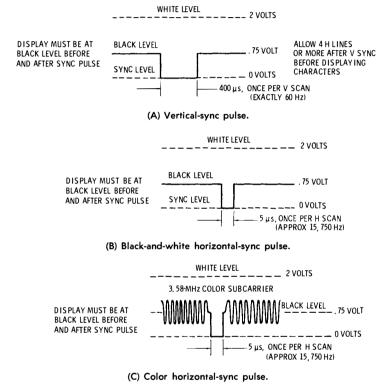

So far we have talked only about dot motions. These motions are controlled by *scanning circuits* that *deflect* the spot to a desired position. Scanning is normally continuous, but we can *synchronize* the start of each horizontal scan and the start of each frame with external *sync* signals. Normally, these horizontal- and vertical-sync signals must be locked together and must be very stable. They do *not* start and stop the scan—all they can do is shorten or lengthen existing scan motions to lock them to an input for synchronization.

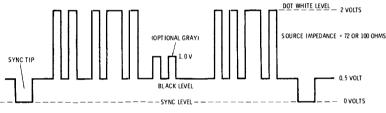

The brightness of the spot is controlled by *video* circuits and *blanking* circuits. Blanking turns the spot off for the return trip on each horizontal scan and frame. Since the corners of a tvt message are just as important as the middle, and since most stock tv sets overscan badly (the scan wraps itself around the side to prevent a black bar, particularly at line-voltage extremes), it is common to use *one third to one half* the scan time for blanking in the horizontal direction. The video circuits determine *how bright* the spot is to be. In broadcasting, variable-level signals are routed to the video amplifier circuitry to provide gray levels. In most tvt's, simple on-off or white-black levels may be supplied instead, to provide dots or no dots as needed.

There is a limit to the number of dots the tv video can handle. This is called the *video bandwidth* or the video response limit. The video portion of a quality color set is some 3 MHz in bandwidth; a black-and-white set can handle 3.5 MHz. Details on where these figures come from appear in Chapter 8. The number of dots per second roughly equals twice the video bandwidth, so a color set can handle six million dots per second, and a black-and-white set can handle seven million dots per second. This sounds like a lot, but if you divide this by the horizontal scan time and allow for blanking and retrace, *the response of an ordinary tv set very much limits the line length and quality of characters you can present*. To beat this problem, you can usually modify the tv, using direct video entry and extending the video response as shown in Chapter 8. It is usually not possible to use clip-on rf entry with long line lengths for this same response-limiting reasoning.

#### **DOT-MATRIX SCANNING**

The important thing to note about television scanning is that we cannot send the dot anywhere we like-all we can do is wait till it comes by and then use it. This is unlike oscilloscopes and premium X-Y displays and is one of the reasons why some tv sets cost much less than some oscilloscopes. We can control only three things: (1) how bright the spot is, (2) when the spot begins the horizontal scan, and (3) when the spot begins a new frame. In fact, (2) and

(3) are further limited in that they must be locked together and cannot be changed much. So, we have to pick a means of character generation that is compatible with the television's normal scanning.

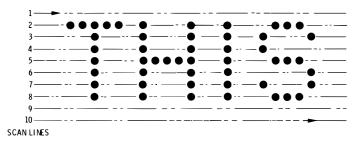

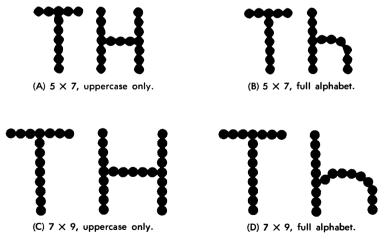

One good approach is called the *dot-matrix* system. Each character is put down as a group of dots or undots. Most tvt's use either a 35-dot character, five dots wide by seven dots high, or a 63-dot character, seven dots wide by nine dots high, with suitable extra undots between characters and character lines.

Fig. 1-7 shows how we dot-matrix scan several letters of a message. On a certain horizontal scan, we put down the top five dots or undots of the first character, skip one or more undots and then put down the top five dots or undots of the second character, and so on across the screen.

Fig. 1-7. Dot-matrix characters on a raster scan.

On the next scan, we put down the five dots or undots of the *second* row of dots in each character, until all our characters are complete. Note that it takes eight to twelve raster lines to present a single row of characters. Also note that we must be able to get each character back at least seven times on successive raster scans, and must be able to do this sixty times over for each second of display time.

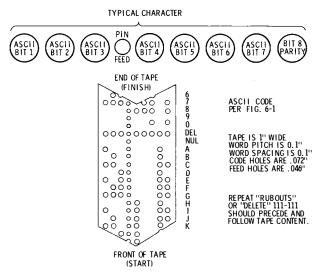

This sure seems like a complicated setup, just to keep one tv set happy. However, it really works out rather simply as the rest of the book will show. Fortunately, we have an integrated circuit, called a *dot-matrix character generator*, that converts the characters, stored in a compact code in the memory, into the dot patterns. This circuit is easily told which portion of which character to get back at any time. The memory normally consists of a random-access memory (RAM). This type of memory is easily told to get characters back, over and over again in the proper sequence needed. As we will see later, what looks like a complex repeat timing problem is solved simply by skipping three outputs on a timing chain divider, and is almost free. There is a standard code that all microprocessors, tv typewriters, and other computer peripherals use. This code is called ASCII, which is short for the American Standard Code for Information Interchange. This code is shown in Table 1-1.

The full ASCII code is normally used as an 8-bit word, either in parallel form by itself or in serial form with additional start and stop bits. The last of these eight bits is reserved for a *parity*, or error-testing, bit. Optionally, this last bit can be used as a cursor or a flag signal, or can be simply ignored.

That leaves us with seven bits. Seven bits can represent  $2^7$ , or 128 different things. In ASCII, we group these  $2^7$  possible codes into

|    | BIT NUMBERS |          |    |          |    |   |               |     |     |        |    |   |                                                                                                                                                    |    |     |

|----|-------------|----------|----|----------|----|---|---------------|-----|-----|--------|----|---|----------------------------------------------------------------------------------------------------------------------------------------------------|----|-----|

| ۱r |             | ····     |    |          | _  |   | $\rightarrow$ | 0   | 0   | 0<br>1 | 0  | 1 | 1<br>0                                                                                                                                             |    | 1   |

| 11 | Γ           | r-       |    |          |    |   | $\rightarrow$ | o   | ĩ   | 0      | 'ı | Ő | ĩ                                                                                                                                                  | 0  | 1   |

| b, | ь<br>Ь      | L_<br>b₅ | b₄ | Ьз       | b2 | Ь | COLUMN        |     |     |        |    |   |                                                                                                                                                    |    |     |

|    |             |          |    |          |    |   | →             | 0   | 1   | 2      | 3  | 4 | 5                                                                                                                                                  | 6  | 7   |

| Ļ  | ↓           | ↓        | Ļ  | <b>↓</b> | ↓  | ↓ | ROW           |     |     |        |    |   |                                                                                                                                                    | L  |     |

|    |             |          | 0  | 0        | 0  | 0 | 0             | NUL | DLE | SP     | 0  | @ | Р                                                                                                                                                  | `. | р   |

|    |             |          | 0  | 0        | 0  | 1 | 1             | SOH | DC1 | !      | 1  | A | Q                                                                                                                                                  | а  | q   |

|    |             |          | 0  | 0        | 1  | 0 | 2             | stx | DC2 | I      | 2  | В | R                                                                                                                                                  | ь  | r   |

|    |             |          | 0  | 0        | 1  | 1 | 3             | ETX | DC3 | ·#     | 3  | с | S                                                                                                                                                  | Ċ  | s   |

|    |             |          | 0  | 1        | 0  | 0 | 4             | EOT | DC4 | \$     | 4  | D | T                                                                                                                                                  | d  | t   |

|    |             |          | 0  | 1        | 0  | 1 | 5             | ENQ | NAK | %      | 5  | E | U                                                                                                                                                  | е  | υ   |

|    |             |          | 0  | 1        | 1  | 0 | 6             | АСК | SYN | &      | .6 | F | v                                                                                                                                                  | f  | v   |

|    |             |          | 0  | 1        | 1  | 1 | 7             | BEL | ETB | ,      | 7  | G | w                                                                                                                                                  | g  | w   |

|    |             |          | 1  | 0        | 0  | 0 | 8             | BS  | CAN | (      | 8  | н | x                                                                                                                                                  | h  | ×   |

|    |             |          | 1  | 0        | 0  | 1 | 9             | нт  | EM  | )      | 9  | I | Y                                                                                                                                                  | i  | у   |

|    |             |          | 1  | 0        | 17 | 0 | 10            | LF  | SUB | *      | :  | J | Z                                                                                                                                                  | i  | z   |

|    |             |          | 1  | 0        | 1  | 1 | 11            | VT  | ESC | +      | ;  | к | [                                                                                                                                                  | k  | {   |

|    |             |          | 1  | 1        | 0  | 0 | 12            | FF  | FS  | ,      | <  | L | $\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{$ | I  | ļ   |

|    |             |          | 1  | 1        | 0  | 1 | 13            | CR  | GS  | -      | =  | Μ | ]                                                                                                                                                  | m  | }   |

|    |             |          | 1  | 1        | 1  | 0 | 14            | so  | RS  | • [    | >  | Ν | ~                                                                                                                                                  | n  | ~   |

|    |             |          | 1  | 1        | 1  | 1 | 15            | SI  | US  | 1      | ?  | 0 | -                                                                                                                                                  | 0  | DEL |

Table 1-1. The Standard ASCII Code Generated by

Most Keyboards

four groups of 32 characters each. Depending on our system complexity, we may or may not use all four of these 32-character groups.

The two groups in the middle of the table make up the upper-case alphabet, the numbers, and some frequently used punctuation. These two groups are sometimes called an ASCII-6 *subset*. They take only six bits to represent their  $2^6 = 64$  different characters. For instance, an ASCII uppercase *H* is coded 00-1000. This is read with the least significant bit (or bit number 1) on the right and the most significant bit (or bit number 6) on the left.

| NUL | NULL                | DLE | DATA LINK ESCAPE       |

|-----|---------------------|-----|------------------------|

| SOH | START OF HEADING    | DC1 | DIRECT CONTROL 1       |

| sтх | START TEXT          | DC2 | DIRECT CONTROL 2       |

| ΕΤΧ | END TEXT            | DC3 | DIRECT CONTROL 3       |

| ΕΟΤ | END OF TRANSMISSION | DC4 | DIRECT CONTROL 4       |

| ENQ | ENQUIRY             | NAK | NEGATIVE ACKNOWLEDGE   |

| ACK | ACKNOWLEDGE         | SYN | SYNCHRONOUS IDLE       |

| BEL | BELL                | ЕТВ | END TRANSMISSION BLOCK |

| BS  | BACKSPACE           | CAN | CANCEL                 |

| нт  | HORIZONTAL TAB      | EM  | END OF MEDIUM          |

| LF  | LINE FEED           | SUB | SUBSTITUTE             |

| νт  | VERTICAL TAB        | ESC | ESCAPE                 |

| FF  | FORM FEED           | FS  | FORM SEPARATOR         |

| CR  | CARRIAGE RETURN     | GS  | GROUP SEPARATOR        |

| so  | SHIFT OUT           | RS  | RECORD SEPARATOR       |

| SI  | SHIFT IN            | บร  | UNIT SEPARATOR         |

Fig. 1-8. ASCII machine commands.

There are several interesting things to note about this ASCII-6 subset. One is that the all zeros 00-0000 code is an "@." When we want a blank or space, either we use the ASCII 10-0000 space code or we disable or blank something between the code and its ultimate output. The second thing to note is that the four least significant bits of the numbers are the same in ASCII, in binary, and in binary-coded decimal (bcd). Thus, to get from a "6" in binary, or a bcd 0110,

we simply "hard wire" two additional ones in front, giving us an ASCII "6," or 11-0110. Note that we need only six bits for the ASCII-6 subset. If we use seven bits instead, the seventh bit is simply the *complement* of bit six, being a one when six is a zero and vice versa.

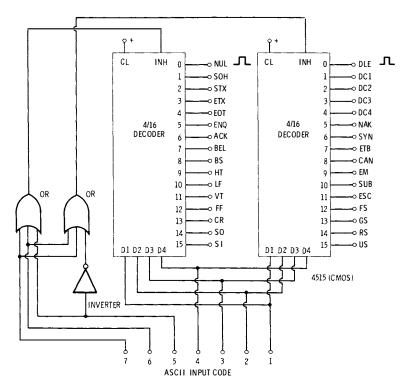

The first 32 code groups in ASCII are called *machine commands* or *control functions*. These are always identified by both bits six and seven being zeros. Machine commands are not usually intended to appear in print or on a screen. Instead, they provide control functions of the support circuitry at either end. These control functions are identified in Fig. 1-8. Typical examples are a carriage return (CR); a backspace (BS); a bell (BEL); an escape (ESC) command that breaks us out of ASCII; and available, but unspecified, direct control lines DC1, DC2, DC3, and DC4.

Generally, tvt's use only a few control functions, so we have the option of choosing how many machine commands we are going to recognize in our system. These options can range from calling *any* machine command a carriage return, through decoding a few needed commands, on up to a complete decoding of all the possible commands. Chapter 5 takes a closer look at these options.

Our final 32 characters are the lowercase alphabet and some infrequently used punctuaion. These are identified by bits six and seven both being a one. These lowercase characters can be used only in a system that has the capability to display lowercase. Note that lowercase characters do not automatically get read as uppercase equivalents if we simply ignore the seventh bit. A simple, logical code change involving bits 6 and 7 (Fig. 6-7) *must* be made if the full ASCII code is input to an uppercase-only output device.

#### **BAUDOT AND SELECTRIC CODES**

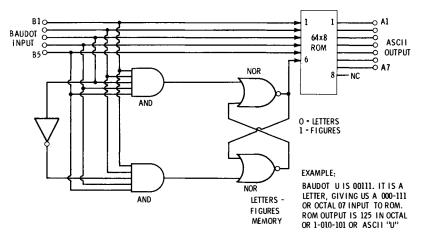

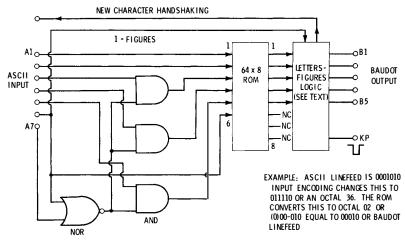

There are two lesser used and specialized codes that sometimes crop up in tvt use. While they are not directly equivalent to ASCII, it is possible to convert them to and from ASCII, with some add-on "repairs" and definitions.

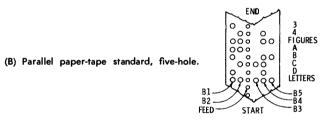

The first of these is the 5-bit *Baudot* code of Table 1-2. Baudot is an obsolete code used with early Teletype machines. It still sees some use in ham rtty and deaf communications systems.

There are only 32 possible code combinations. To get more characters, there are two *shift* commands—a *letters* shift and a *figures* shift. These almost double the number of available characters, but you have to keep track of what the past history of the code was. You have to shift to letters for letters and figures for figures. Baudot is further complicated by the punctuation symbols, which differ, depending on whether the machine was originally used by the military, the weather service, telex, twx, or stock quotation services. More

|   | Code<br>Bits |   |   |   |           |           | Code<br>Bits |   |   |   |   |         |          |

|---|--------------|---|---|---|-----------|-----------|--------------|---|---|---|---|---------|----------|

| 5 | 4            | 3 | 2 | 1 | Letters   | Figures   | 5            | 4 | 3 | 2 | 1 | Letters | Figures* |

| 0 | 0            | 0 | 0 | 0 | Blank     | Blank     | 1            | 0 | 0 | 0 | 0 | т       | 5        |

| 0 | 0            | 0 | 0 | 1 | E         | 3         | 1            | 0 | 0 | 0 | 1 | z       | "        |

| 0 | 0            | 0 | 1 | 0 | Linefeed  | Linefeed  | 1            | 0 | 0 | 1 | 0 | L       |          |

| 0 | 0            | 0 | 1 | 1 | A         | _         | 1            | 0 | 0 | 1 | 1 | w       | 2        |

| 0 | 0            | 1 | 0 | 0 | Space     | Space     | 1            | 0 | 1 | 0 | 0 | н       | #        |

| 0 | 0            | 1 | 0 | 1 | S         | Bell      | 1            | 0 | 1 | 0 | 1 | Y       | 6        |

| 0 | 0            | 1 | 1 | 0 | 1         | 8         | 1            | 0 | 1 | 1 | 0 | Р       | g i      |

| 0 | 0            | 1 | 1 | 1 | U         | 7         | 1            | 0 | 1 | 1 | 1 | Q       | 1        |

| 0 | 1            | 0 | 0 | 0 | Car. Ret. | Car. Ret. | 1            | 1 | 0 | 0 | 0 | 0       | 9        |

| 0 | 1            | 0 | 0 | 1 | D         | \$        | 1            | 1 | 0 | 0 | 1 | В       | ?        |

| 0 | 1            | 0 | 1 | 0 | R         | 4         | 1            | 1 | 0 | 1 | 0 | G       | &        |

| 0 | 1            | 0 | 1 | 1 | J         | ,         | 1            | 1 | 0 | 1 | 1 | Figures | Figures  |

| 0 | 1            | 1 | 0 | 0 | N         | ,         | 1            | 1 | 1 | 0 | 0 | M       | .        |

| 0 | 1            | 1 | 0 | 1 | F         | !         | 1            | 1 | 1 | 0 | 1 | х       |          |

| 0 | 1            | 1 | 1 | 0 | с         | :         | 1            | ĺ | 1 | 1 | 0 | v       | ;        |

| 0 | 1            | 1 | 1 | 1 | к         | (         | 1            | 1 | 1 | 1 | 1 | Letters | Letters  |

Table 1-2. Baudot Code

\* "Figures" punctuation may vary, depending on original use of machine.

Table 1-3. Selectric Code

|        | R<br>T<br>T |         | ;       | 0<br>0<br>0 | 0<br>0<br>1 | 0<br>1<br>0           | 0<br>1<br>1 | 1<br>0<br>0 | 1<br>0<br>1 | 1<br>1<br>0 | 1<br>1<br>1 |                            |

|--------|-------------|---------|---------|-------------|-------------|-----------------------|-------------|-------------|-------------|-------------|-------------|----------------------------|

| s<br>↓ | R2A<br>↓    | R2<br>↓ | R1<br>∔ |             |             |                       |             |             |             |             |             |                            |

| 0      | 0           | 0       | 0       | -           | ь           | ×                     | 9           |             |             |             |             |                            |

| 0      | 0           | 0       | 1       | У           | h           | s                     | ¢           | /           | 1           | 0           | 4           |                            |

| 0      | 0           | 1       | 0       |             |             |                       |             |             |             |             |             |                            |

| 0      | 0           | 1       | 1       |             |             |                       |             |             |             |             |             |                            |

| 0      | 1           | 0       | 0       | q           | k           | i.                    | 6           | ,           | с           | a           | 8           | 1 lowercase                |

| 0      | 1           | 0       | 1       | р           | e           | ,                     | 5           | ;           | d           | r           | 7           |                            |

| 0      | 1           | 0       | 0       | =           | n           |                       | 2           | f           | u           | v           | 3           |                            |

| 0      | 1           | 1       | 1       | j           | t           | 1 <u>2</u> !          | z           | 9           | ×           | m           | 1           |                            |

| 1      | 0           | 0       | 0       |             | в           | w                     | (           |             |             |             |             |                            |

| 1      | 0           | 0       | 1       | Y           | н           | s                     | )           | ?           | L           | 0           | \$          |                            |

| 1      | 0           | 1       | 0       |             |             |                       |             |             |             |             |             |                            |

| 1      | 0           | 1       | 1       |             |             |                       |             |             |             |             |             |                            |

| 1      | 1           | 0       | 0       | Q           | к           | Т                     | ¢           | ,           | с           | A           | *           | UPPERCASE                  |

| 1      | 1           | 0       | 1       | Р           | E           |                       | %           | :           | D           | R           | &           | = REDUNDANT<br>OR NOT USED |

| 1      | 1           | 1       | 0       | +           | N           |                       | 0           | F           | υ           | v           |             |                            |

| 1      | 1           | 1       | 1       | J           | т           | $\frac{1}{4}^{\circ}$ | z           | G           | x           | м           | ŧĮ          |                            |

details on this code and its conversion to and from ASCII appear in the last chapter.

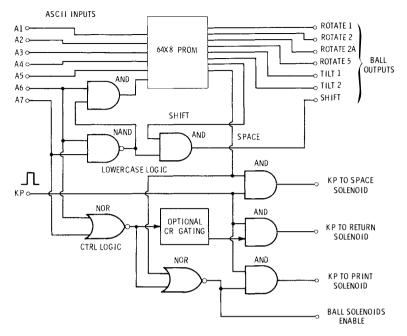

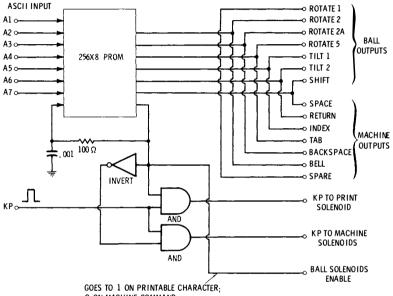

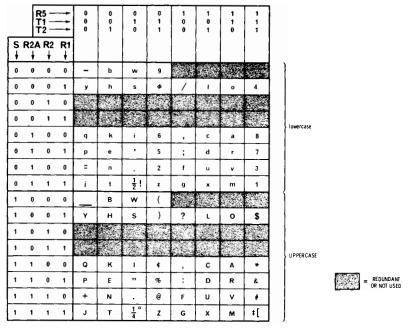

The Selectric code of Table 1-3 is associated with the Selectric office typewriters and the Selectric computer i/o machines, and is important whenever you are adapting an office typewriter for tvt hard copy, following the guidelines of Chapters 3 and 9. There are seven bits to this code, but not all possible code combinations are used. One of these bits is called a *shift* bit. It gives us the ability to handle uppercase or lowercase information, usually with a  $180^{\circ}$  rotation of the typing ball. The remaining bits in the code are named after their effect on ball positioning and are coded by the Selectric code bails. These are called Rotate 1, 2, 2A, 5, and Tilt 1 and 2.

Unlike ASCII, machine commands are external to this code. They include space, return, backspace, tab, bell, and index. Note that space is treated as a character in ASCII and as a machine command in Selectric.

#### SOME TERMS

Let's now take a quick look at some of the concepts, terms, and acronyms that are associated with tvt systems:

- address—A particular location in a memory.

- ASCII—An acronym for American Standard Code for Information Interchange. Standard code used in tvt's, microcomputers, and peripheral devices. See Table 1-1.

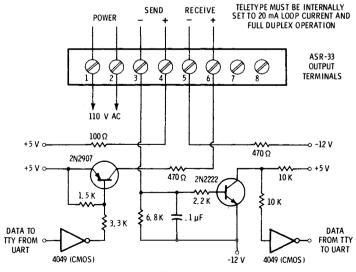

- ASR33—Automatic Send-Receive Computer Teletype. See Chapter 9.

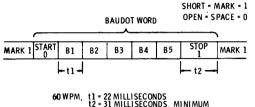

- asynchronous—A form of serial data transmission in which the spacing between words can be random and unpredictable. Asynchronous transmission is commonly used with tvt interfaces. Start and stop bits must be added to a character before transmission. See Chapter 7.

- baud rate—The speed at which 1's and 0's are sent through a serial interface. Common baud rates are 110, 150, 300, 600, and 1200 bits per second.

- Baudot-An obsolete 5-bit Teletype code. See Table 1-2 and Chapter 9.

- bit position error—A displacement of a received data bit, in which the data bit is ahead of or behind where it is expected to be. Often caused by group delay distortion in modem channels.

- bit rate error—A received data bit stream that is faster or slower than it is expected to be. Often caused by speed variations in cassette recorders.

- blanking—Making a display black by turning off the video. Used during retrace and to format data.

- bounceless contact—A mechanical contact that has been conditioned with a flip-flop or monostable to eliminate all contact noise during make and break.

- bus organization—A system sharing a common set of communications lines among several devices. In a *unidirectional bus system*, signals from one or more sources, *activated one at a time*, drive a common load or loads. Addressing a tvt memory internally, from a cursor or from an external microcomputer, is one example. A *bidirectional bus system* lets signals go either way on the bus, again activated only one at a time. Most microprocessor data buses are bidirectional.

- character generator—A circuit that converts characters stored in ASCII into dot patterns suitable for tvt display.

- class-1 tv device—Legal classification of clip-on rf entry modulators. See Chapter 8.

- CMOS—An acronym for Complementary Metal-Oxide Semiconductor. A micropower logic family that is widely available and low in cost.

- code converter—A read-only memory or other system set up to convert one code to another. Typical examples are ASCII/Selectric, Baudot/ASCII, and ASCII/ Baudot conversions.

- color subcarrier—A 3.58-MHz signal added to the composite video whose phase sets the received color and whose amplitude sets the color saturation.

- cursor—A circuit used to keep track of which character is entered next in a tvt and to display that character location. Typical cursors include the *count and compare*, the *McFadden*, and *microprocessor-based systems*.

- data-The information that is to be displayed on a tvt.

- DMA (direct memory access)—Any system for rapidly changing the contents of a memory by means of an external set of control signals.

- direct video—Presenting information to a tv set by entering it into the video circuitry, usually by way of an added jack and changeover switch.

- dot matrix—A method of generating characters by converting the ASCII code into a suitable group of dots arranged in a  $5 \times 7$ ,  $7 \times 9$ , or other suitable patterned array.

- encoder—A circuit used to convert the single switch closures of a keyboard into a composite ASCII or other code.

- **EPROM**—A read-only memory that can be both programmed and erased in the field. Bulk erasure is often done with strong ultraviolet light.

- full duplex—Operating a communications channel in both directions at the same time without interference.

- graphics—Using a tvt to display lines, patterns, art forms, and symbols, rather than its standard alphanumeric letters and numbers mode. Both modes can be combined.

- group delay distortion—A hard-to-eliminate filter property that speeds up or slows down 1's with respect to 0's in a communications channel. A key design problem in modems.

- half duplex—Taking turns operating a communications channel in one direction at a time.

- handshaking—A communications interface in which the receiver asks for a signal, accepts it, and then acknowledges it. Handshaking prevents ignored and overrun signalling between devices.

- hard copy-Any reasonably permanent form of printed data or other record.

- hardware—The physical circuitry of a tvt or microcomputer.

- hot chassis—A television set that has its chassis connected to one side of the power line, thus creating a safety hazard. See Chapter 8.

- interface—A circuit used to get between two systems having different requirements. Serial interface is often used to communicate with cassette systems, modems, and Teletypes.

- i/o-Input/output.

- k-Symbol for 1024 bits. A 4k memory has 4096 bits.

- keyboard-Standard method of manual data entry into a tvt. See Chapter 6.

- mark—A digital logic 1 or a shorted transmission line.

- memory—Circuits capable of remembering data or sequential operating procedures.

- microprocessor—A "computer-on-a-chip" integrated circuit usually set up to move information from inputs, into and out of related memory circuits, and then to feed it into one or more *peripheral* devices, usually following a specified sequence or program.

- microprogramming—Any "hard-wired" way of carrying out a sequential routine on a computer, microcomputer, or microprocessor. The alternative is software programming in which stored but changeable instructions are used.

- modem—Acronym for *mo*dulator-*dem*odulator. A means of getting data onto and back from a telephone line or other communications channel.

- MOS—Metal-Oxide Semiconductor. A family of integrated circuits and their technology that lends itself well to tvt and microcomputer uses. They are normally used in larger subsystems called LSI, or large-scale integration, and have very high input impedances and medium speeds.

- page—A full screen of tvt information.

- parallel—An arrangement of data or addresses in which all the bits are simultaneously available on multiple lines.

- parity—An error-testing technique. An extra bit called a parity bit is added to a word. The parity bit makes each of the 1's in the word an even number. After transmission and reception, parity can be tested. An error has happened if the 1's are now odd. Alternatively, a system can be set up for odd parity with the same results. Simple parity can indicate but not repair errors.

- peripheral device-A device that attaches to a computer or microprocessor, let-

ting it perform useful tasks. Typical examples are tvt's, hard-copy printers, modems, cassette storage, etc.

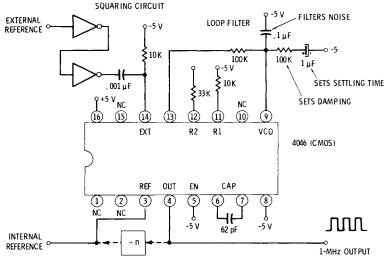

- phase-locked loop—A circuit that locks some system timing to an externally provided reference. Used in tvt's to lock system timing to the power line for a stable display or to an existing video program for titling and annotation.

- programming—Defining the operating sequences that a computer or microprocessor is to follow.

- PROM—Acronym for Programmable Read-Only Memory. An integrated circuit that can have its internal memory patterns changed in the field but is otherwise nonvolatile. See Chapter 3.

- RAM—Acronym for Random-Access Memory. An integrated circuit that can have its internal memory patterns rapidly changed at system speeds in any sequence. Normally volatile. See Chapter 3.

- raster—The repetitive sequence of scan lines on a television set. See Fig. 1-6.

- read—To interrogate the contents of a memory without changing the contents, or to provide an output *from* memory or another source.

- refresh—To make information available over and over again as needed to meet the timing needs of a dynamic memory or a tv raster scan display.

- rf entry—Presenting information to a tv set by entering it into the tuner via the antenna terminals, usually by way of a class-1 tv device.

- rollover—A keyboard encoding technique that minimizes errors. Two-key rollover allows any two keys to be down at once without error. N-key roll-over allows any number of keys to be down at once without error but is complex and has system limitatitons. See Chapter 6.

- RS232C—A very old EIA interface standard that is commonly used by peripheral devices on larger computer systems. See Chapter 7.

- screen read—An optional tvt circuit that allows the displayed message to be retransmitted to a microcomputer or peripheral device. Used to format data for cassette storage and to edit programs.

- Selectric—IBM office typewriter or computer input/output device using the Selectric code of Fig. 1-9.

- serial—An arrangement of data or characters in which the bits are made sequentially available on a single line.

- sidetone—"Hear yourself" feedback common in phone systems. A serious problem in modern design. See Chapter 7.

- software—The programming, documentation, and specified paper sequences of operation that allow a computer or microcomputer system to work.

- space—A digital logic 0 or an open transmission line.

- speed tolerant—A type of cassette recording system that allows changes in recorder speed from machine to machine or from time to time as batteries age or as line voltages change, and that does so without introducing errors.

- start bit—A signal bit, usually a 0, that precedes a word to be sent in an asynchronous data system.

- stop bit—One or more signal bits, usually a 1, that follow a word just sent in an asynchronous data system.

- sync—The vertical and horizontal synchronizing pulses that tell a tv display when to start each horizontal line and each frame.

- synchronous—A form of serial data transmission in which the spacing between words is locked to system timing and a constant. Not commonly used in tvt work.

- system timing—The TTL or CMOS integrated circuitry that converts characters stored in a memory into a repetitive form that a tv set can use.

- TTL—Acronym for transistor-transistor logic. A fast digital-logic family that is widely available and low in cost. See the *TTL Cookbook*, also by this author and published by Howard W. Sams & Co., Inc.

- tvt—Abbreviation for a tv typewriter. Any low-cost way of displaying lots of words, numbers, or graphics on an ordinary tv set.

- UART—Acronym for Universal Asynchronous Receiver Transmitter. An integrated circuit used to convert data from parallel to serial form and back again. Covered in detail in Chapter 7.

- update—To change part or all of the message displayed on a tvt. A frame-rate update usually adds or drops one character per frame. A DMA update usually changes the entire screen in one frame time.

- video-The brightness and color information fed to a television set.

- video bandwidth—The maximum number of dots per second that a television set can display. The video bandwidth for an unmodified color tv is 3 MHz, while the bandwidth of an unmodified black-and-white tv is 3.5 MHz. These correspond to 6 and 7 million dots per second, respectively. See Chapter 8.

- word—A grouping of bits representing a character or command. Most tvt systems use words of six to eight bits.

- write—To place information into a memory, changing the memory contents. To provide an input from another source to memory.

#### CHAPTER 2

## Integrated Circuits for TVT Use

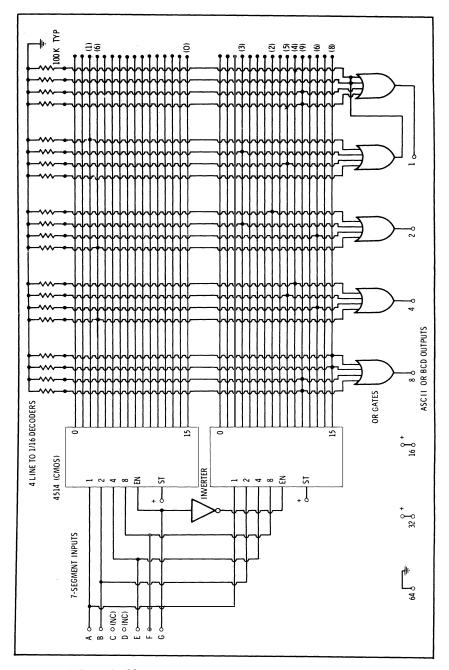

In this chapter, we will take a detailed look at some representative samples of integrated circuits suitable for tvt uses. The seven basic types of circuits that we will be looking at are *baud-rate generators*, *character generators*, *keyboard encoders*, *line drivers and receivers*, *programmable read-only memories*, *random-access memories*, and *serial interface UARTs*.

Besides these devices, there are other types of integrated circuits that you will often be using in tvt circuits. A general-purpose digital logic family such as TTL or CMOS is almost essential for system timing and to "glue" the rest of the works together. CMOS is often the best choice for new designs.

Dedicated integrated circuits are also available that are intended to work within a specific microprocessor family. Often these are simply modifications of the ICs we will be looking at in this chapter. More details on these specialized circuits are available from their respective manufacturers.

Sources for the circuits in this chapter and alternates to them appear in Chart 2-1. Always be sure to have manufacturers' data sheets on hand whenever you are testing or using these devices.

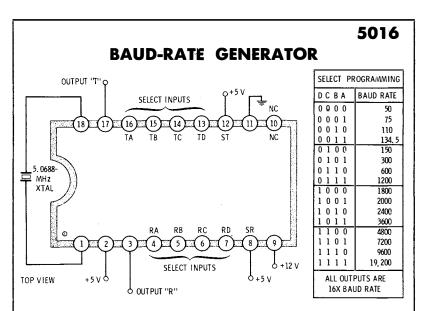

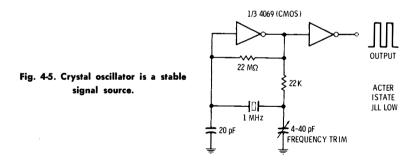

#### **BAUD-RATE GENERATORS**

Baud-rate generators are used to provide the reference frequencies needed by serial interface devices, such as UARTs, telephone modems, Teletypes, and cassettes. They have the advantages of adjustment-free crystal stability and multiple output frequencies that are easily changed.

## Chart 2-1. Some Integrated Circuit Manufacturers

| Advanced Micro Devices                                                     | MOS Technology, Inc.                                                                             |  |  |  |  |

|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--|--|--|--|

| 901 Thompson Place                                                         | 950 Rittenhouse Road                                                                             |  |  |  |  |

| Sunnyvale, CA 94086                                                        | Norristown, PA 19401                                                                             |  |  |  |  |

| American Microsystems, Inc.                                                | Mostek Corporation                                                                               |  |  |  |  |

| 3800 Homestead Road                                                        | 1215 West Crosby Road                                                                            |  |  |  |  |

| Santa Clara, CA 95051                                                      | Carrollton, TX 75006                                                                             |  |  |  |  |

| Cal-Tex Semiconductor                                                      | Motorola Semiconductor                                                                           |  |  |  |  |

| 3090 Alfred Street                                                         | Products, Inc.                                                                                   |  |  |  |  |

| Santa Clara, CA 95950                                                      | Box 20912                                                                                        |  |  |  |  |

| Cermetek, Inc.<br>660 National Avenue<br>Mountain View, CA 94040           | Phoenix, AZ 85036<br>National Semiconductor<br>2900 Semiconductor Drive<br>Santa Clara, CA 95051 |  |  |  |  |

| Electronic Arrays, Inc.                                                    | Nitron Corporation                                                                               |  |  |  |  |

| 550 East Middlefield Road                                                  | 10420 Bubb Road                                                                                  |  |  |  |  |

| Mountain View, CA 94043                                                    | Cupertino, CA 95014                                                                              |  |  |  |  |

| Exar Integrated Systems, Inc.<br>750 Palomar Avenue<br>Sunnyvale, CA 94086 | RCA Solid State Division<br>Somerville, NJ 08876                                                 |  |  |  |  |

| Fairchild Semiconductor                                                    | Rockwell International                                                                           |  |  |  |  |

| 464 Ellis Street                                                           | Microelectronic Device Div.                                                                      |  |  |  |  |

| Mountain View, CA 94040                                                    | 3310 Miraloma Avenue                                                                             |  |  |  |  |

| General Instrument Corporation                                             | Anaheim, CA 92803                                                                                |  |  |  |  |

| 600 West John Street                                                       | Signetics                                                                                        |  |  |  |  |

| Hicksville, NY 11802                                                       | 811 East Arques Avenue                                                                           |  |  |  |  |

| Harris Semiconductor<br>Box 883<br>Melbourne, FL 32901                     | Sunnyvale, CA 94086<br>SMC Microsystems<br>35 Marcus Boulevard<br>Hauppauge, NY 11787            |  |  |  |  |

| Intel Corporation                                                          | Synertek                                                                                         |  |  |  |  |

| 3065 Bowers Avenue                                                         | 3050 Coronado Drive                                                                              |  |  |  |  |

| Santa Clara, CA 95051                                                      | Santa Clara, CA 95051                                                                            |  |  |  |  |

| Intersil, Inc.                                                             | Texas Instruments                                                                                |  |  |  |  |

| 10900 North Tantau Avenue                                                  | Box 5012                                                                                         |  |  |  |  |

| Cupertino, CA 95014                                                        | Dallas, TX 75222                                                                                 |  |  |  |  |

| Monolithic Memories, Inc.                                                  | Western Digital Corporation                                                                      |  |  |  |  |

| 1165 East Arques Avenue                                                    | 3128 Red Hill Avenue                                                                             |  |  |  |  |

| Sunnyvale, CA 94086                                                        | Newport Beach, CA 92663                                                                          |  |  |  |  |

|                                                                            |                                                                                                  |  |  |  |  |

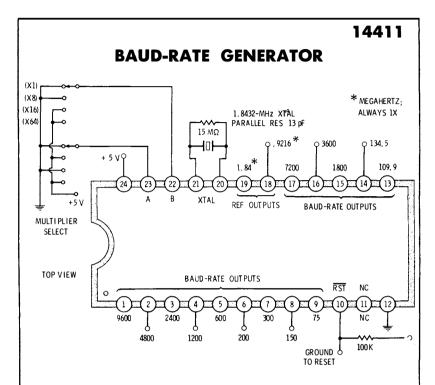

The 5016 is a Standard Microsystems product in an 18-pin package that produces a selected pair of standard  $16 \times$  reference frequencies. The 14411, made by Motorola, comes in a 24-pin package. It simultaneously produces 16 different reference frequencies, available as  $1 \times$ ,  $8 \times$ ,  $16 \times$ , or  $64 \times$ .

#### CHARACTER GENERATORS

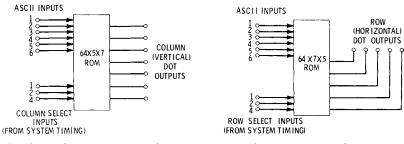

Character generators convert a stored ASCII character and some timing commands into a group of dots suitable for raster scan tv display.

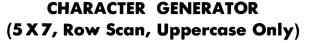

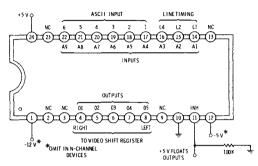

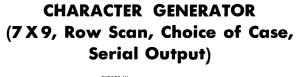

The 2513 is a utility  $5 \times 7$ , 64-character device by Signetics and General Instruments. The GI device needs only a single +5-V supply but may not be compatible with a CMOS video output shift register working on a higher supply voltage or on a split +5-V, -5-V supply. The 5004 is a Standard Microsystems product. It works on a single +5-V supply and has internal storage and output registers. It provides a premium  $7 \times 9$  dot matrix of uppercase and lowercase characters. The 6072 is a very fast, single-supply  $7 \times 9$  matrix of 128 characters offered by Monolithic Memories.

#### **KEYBOARD ENCODERS**

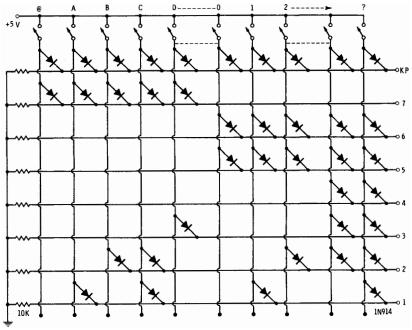

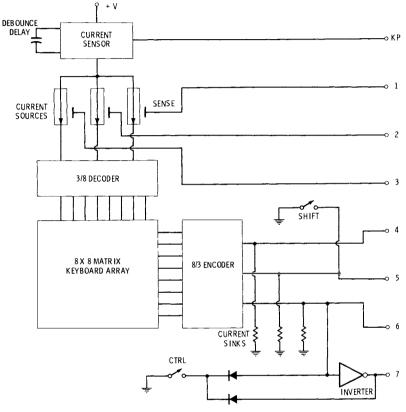

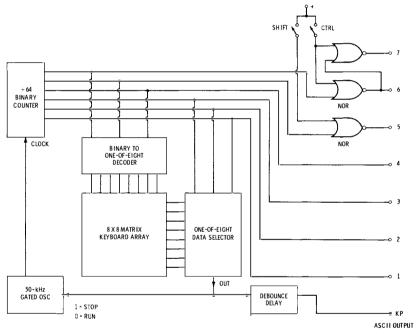

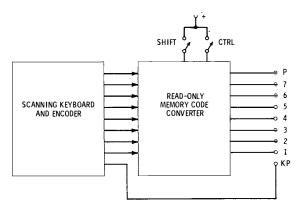

Keyboard encoders convert single-contact closures of a keyswitch into a composite, debounced, and properly shifted ASCII code. Output is usually in parallel form with parity.

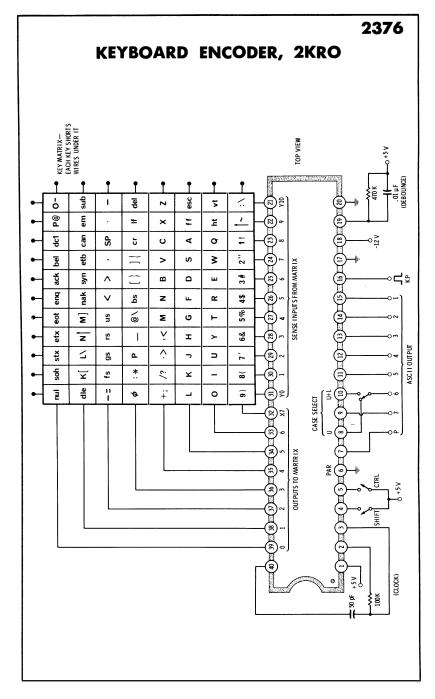

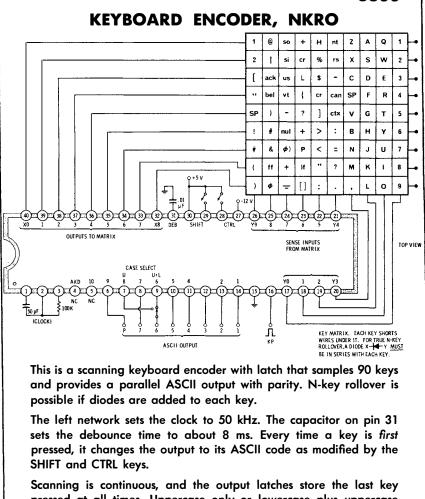

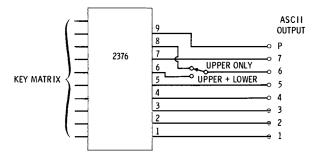

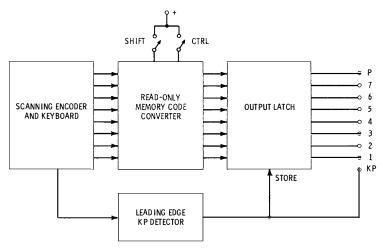

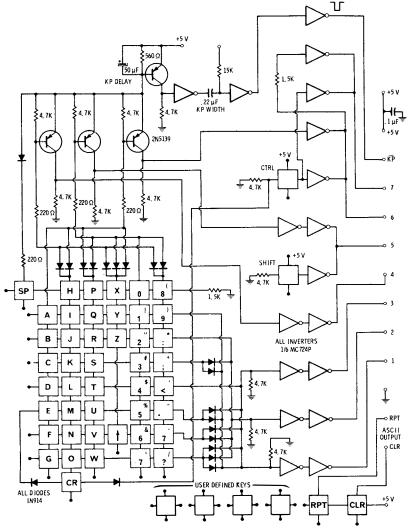

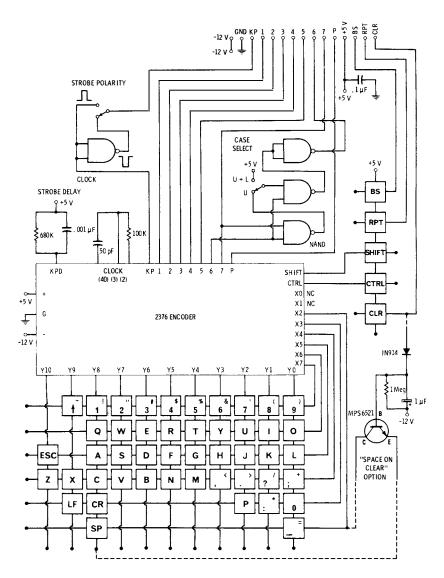

The 2376 is an 88-key encoder with two-key rollover and a choice of uppercase only or uppercase plus lowercase output. The 3600 is a 90-key encoder that allows true n-key rollover, provided diodes are added to each keyswitch. Both devices are available from General Instruments and Standard Microsystems.

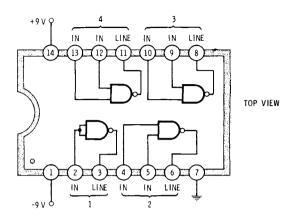

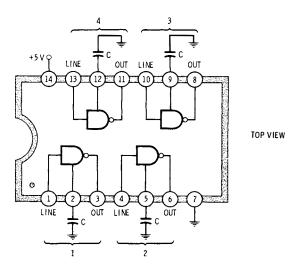

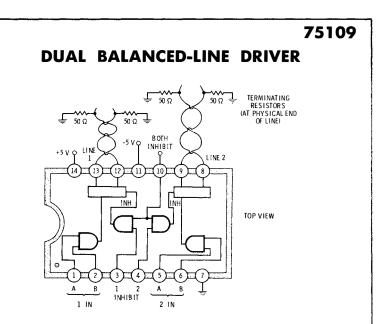

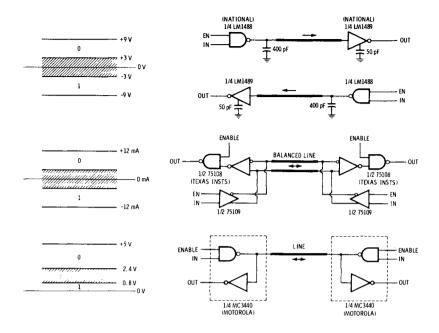

#### LINE DRIVERS AND RECEIVERS

Line drivers and receivers are used to "amplify" 1's and 0's so that lots of loads can be driven and so that wiring capacitance and cable runs do not adversely slow down system speeds. They are also used to send signals long distances over wired serial interfaces.

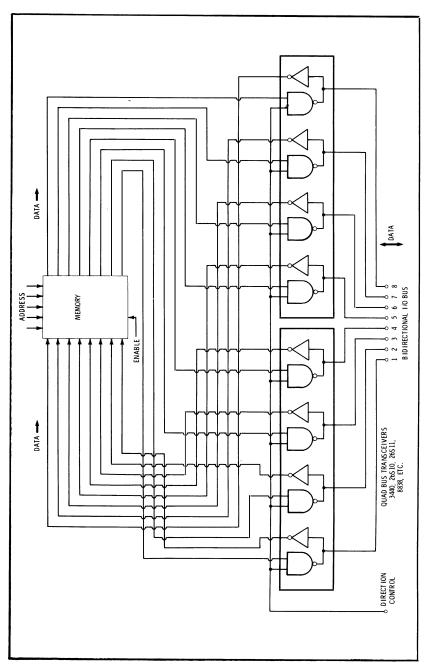

There are many of these devices available. The major manufacturers include Advanced Micro Devices, Fairchild, National, Texas Instruments, Motorola, and Signetics.

The 26S10 is a quad bidirectional bus transceiver user for twoway microprocessor interface by Advanced Micro Devices. Similar devices are the Motorola 3443 and the Texas Instruments 75138, while the National 8838 does the same thing with a different pinout. The 1488 and 1489 are an older pair of devices for RS232-C interfacing. The 1488 is a quad-line driver, while the 1489 is a quad-line receiver. Suppliers include Advanced Micro Devices, Motorola, and Texas Instruments.

The 75107 and 75109 are dual receivers and transmitters for differential data transmission over long distances. Suppliers include AMD and TI.

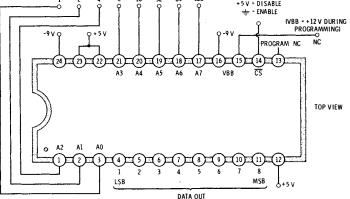

#### **PROGRAMMABLE READ-ONLY MEMORIES**

Programmable ROMs are used for storing microprocessor programs, for code conversions, and for customized, "you-program-it," nonvolatile logic arrays.

The 1702 is a 2048-bit MOS programmable read-only memory organized as 256 eight-bit words. It can be electrically bulk-erased by placing it under intense ultraviolet light. Sources include Intel and Advanced Micro Devices. A similar device is the National 5202.

The 5600 is an Intersil bipolar programmable read-only memory arranged as 32 eight-bit words and having a 50-ns access time. Similar devices include the National 5330, the Texas Instruments 74188, and the Harris 8256.

#### RANDOM-ACCESS MEMORIES

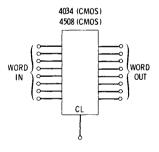

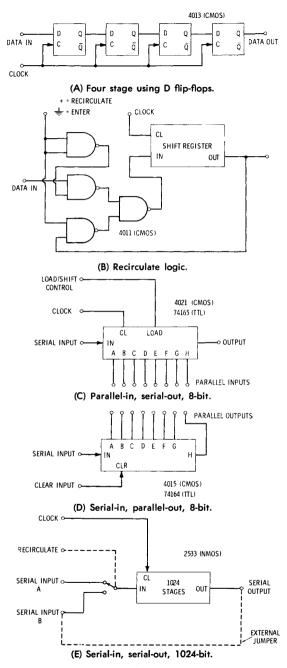

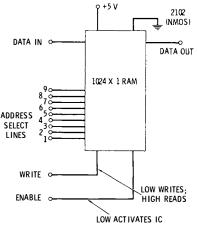

We use random-access memories, or RAMs, for character storage in tvt's and for microprocessor data storage. Static 1024-bit devices are often the best choice for these applications.

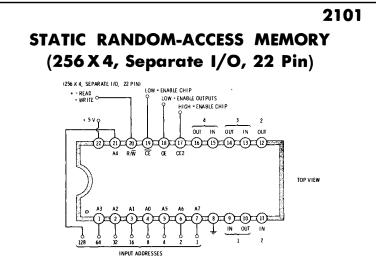

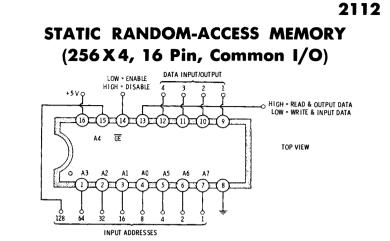

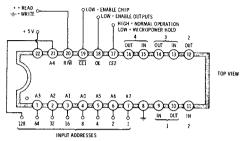

The 2101 is arranged as 256 four-bit words and is in a 22-pin package. It has separate input and output leads. It is made by Intel, Advanced Micro Devices, and Synertek. The Texas Instruments 4039 is a similar device.

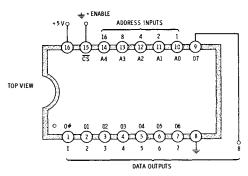

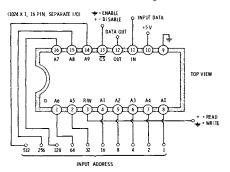

The 2102 is arranged as 1024 one-bit words and is in a 16-pin package with separate input and output leads. Sources include Intel, Advanced Micro Devices, Fairchild, and Synertek. It is also known as the Intersil 7552, the Signetics 2602, and the Texas Instruments 4033.

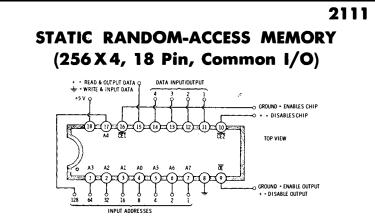

The 2111 is arranged as 256 four-bit words and is in an 18-lead package. It has common input/output leads and an output disable. Sources include Intel, American Micro Devices, and Synertek, along with the Texas Instruments 4042.

The 2112 is similar to the 2111 except that it is in a 16-pin package and has no output disable. Sources are similar to the 2111 except that the Texas Instruments part number is 4033 and it is also offered by Signetics as a 2602. The Intel 5101 is a premium micropower 2101 using CMOS technology. It is useful for nonvolatile memory systems using standby battery-power backup.

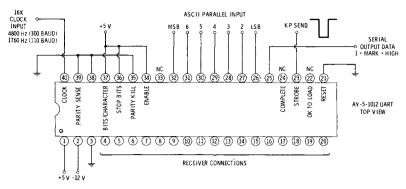

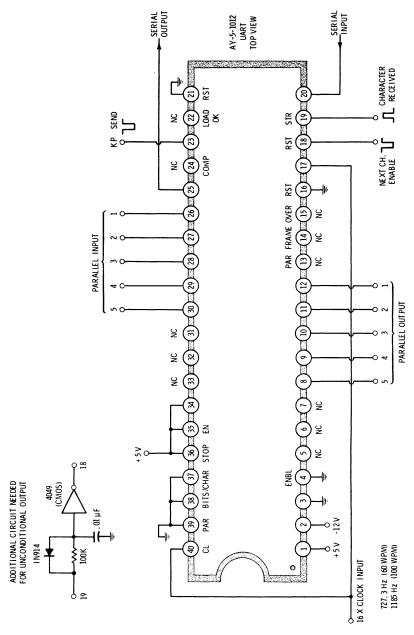

#### SERIAL INTERFACE UARTS

A UART, or universal asynchronous receiver transmitter, is used for serial-to-parallel and back again conversion to interface a serialoperating device, such as a Teletype, a cassette storage system, or a modem, with the parallel input/output lines of a tvt or a microcomputer.

The 1013 is a general instruments device. It is also available as a 1014 working off a single 5-V supply. Other similar devices include the American Microsystems S1883, the Signetics 2536, the Standard Microsystems 2502, the Texas Instruments 6012, and the Western Digital 1602.

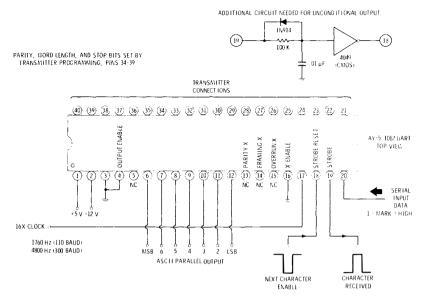

This integrated circuit simultaneously generates two reference frequencies useful in tvt, serial interface, and microprocessor applications. The two selected frequencies may be rapidly changed either by manual control or under software control.

In normal operation, pins 2, 8, and 12 are made +5 V, and +12 V is applied to pin 9. A 5.0688-MHz crystal is connected as shown. Output frequencies are selected by the A, B, C, and D inputs following the chart at the right. A 0 is a grounded input; a 1 is +5 V. Each output can drive two TTL loads or any number of CMOS loads.

The transmitter side of a serial interface is normally associated with the higher or T pins, while the receiver side uses the lower or R pins. This choice is arbitrary.

Select inputs need not be applied continuously if a latched mode is used. To latch, bring pins 8 and 12 low. Apply the A,B,C,D code and briefly bring pin 8 or 12 high, returning it to ground after selection. The chip will now hold the selected code. Pin 8 low holds the T selection; pin 8 high follows the T selection. Pin 12 does the same for the R selection.

All outputs are symmetrical 50-50 duty cycle except for 9600, which is 48-52. All outputs are sixteen times the baud rate. Slight frequency errors exist on the 134.5, 2000, and 19,200 baud-rate outputs; these are rarely used.

Supply current is 10 mA from the +12-V supply and 28-mA from the +5-V supply.

This integrated circuit simultaneously generates 16 reference frequencies useful in tvt, serial interface, and microprocessor applications.

In normal operation, pins 10 and 24 are made +5 V. Pins 22 and 23 are programmed as shown, to output frequencies that are 1X, 8X, 16X, or 64X those shown on pins 1 through 9 and 13 through 17. Each of these outputs can drive one TTL load or any number of CMOS loads.

Frequency is set by the parallel-resonant 1.8432-MHz crystal and bias resistor on pins 20 and 21. The crystal frequency appears as an output on pin 19, and half that frequency appears at pin 18, independent of the multiplier settings. These outputs are useful for microprocessor clocks, both single and two-phase.

All outputs may be reset to zero by bringing pin 10 low. In normal operation, pin 10 must be held high.

Typical supply current is 2 mA plus one additional milliampere for each output connected to a TTL load.

All outputs are symmetrical with a 50-50 duty cycle.

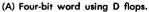

## 2513

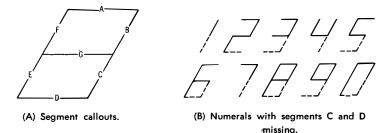

This circuit provides the dot-matrix patterns needed for raster scan display of ASCII characters. It uses a  $5 \times 7$  matrix of uppercaseonly characters and is a row scan device intended for normal tv use.

In normal operation, supply power is applied as shown and pin 11 is allowed to be at ground. The ASCII code is input to pins 17 through 22. Line timing is applied to pins 14 through 16. A 000 on these lines selects all blank outputs. A 001 on these lines puts out the dots for the first, or top, row of the character. A 010 puts out the second from the top row of dots, continuing to a 111 output that puts out the bottom, or seventh, row of dots.

The output is routed to a video shift register, arranged so that the left-most dot, 05, goes nearest the serial output of the shift register.

The N-channel versions of this device need no -5-V or -12-V supplies but are unable to accept or provide outputs that swing below ground.

Access time is 400 ns after all address inputs are stable.

Placing +5 V on pin 11 floats the output. This produces a white or 1 output when connected to TTL. It produces a white or 1 output when connected to CMOS with pull-up resistors, and produces a black or 0 output when connected to CMOS with pull-down resistors.

Operating current is 25 mA for a 5-V device and 12 mA from each supply for the +5-V, -12-V devices.

Note that loading of the output character must be delayed from the input address changes by at least the access time. Chapters 3 and 4 have more-detailed information on using character generators.

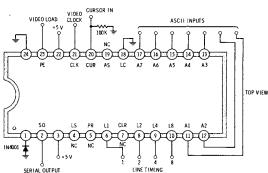

## 5004

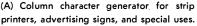

This is a premium dot matrix, row-scan character generator. It has its own internal shift register and directly produces output serial video.

In normal operation, a video clock that sets the dot rate is input to pin 21. A normally low video load command is input to pin 23, which briefly goes high whenever you want to transfer a new set of dots to the output register. The video clock should be eight times the frequency of the video load for one undot between characters, nine times for two undots, and ten times for three undots.

Line timing is applied weighted 1, 2, 4, 8 as shown, and the ASCII code is input on the A1 through A7 lines. Serial video, ready for sync combination, appears as an output on pin 2.

There are many use options. The line timing may be strobed into the chip by grounding pin 4 during the hold times. The ASCII character may be strobed into the chip by grounding pin 19. Lowercase may be inhibited by making pin 18 positive. A positive input to pin 20 replaces the character with a cursor box.

Access time is typically 750 ns. Power-supply current is 75 mA. Note the unusual supply connections, particularly the ground on pin 24. Pin 1 controls an internal charge pump to bias the substrate at -0.6 V.

Pin 5 will force the output high. Pin 7 will force the output low. Pins 5 and 7 high together will float the output. This can simplify video combination.

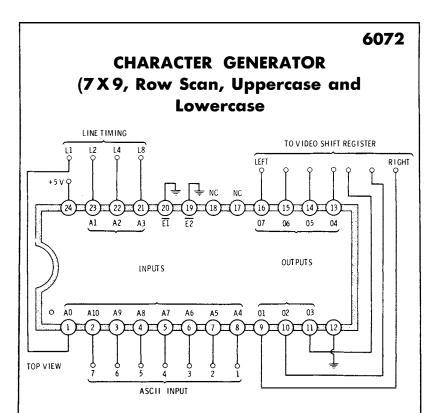

This is a premium device that provides the dot-matrix patterns needed for raster scan display of ASCII characters. It uses a  $7 \times 9$  matrix of uppercase and lowercase characters and is a row scan device intended for normal tv use.

For normal operation, the ASCII code is routed to pins 2 through 8, and line timing signals weighted 1, 2, 4, 8 are routed to pins 1, 23, 22, and 21. Pins 20 and 19 are grounded, and supply power is applied to pin 24. The line timing selects which line of character dots is to be output.

The output dot combinations appear on pins 9, 10, 11, 13, 14, 15, and 16 in the order noted. They are routed to a video-output shift register for serial conversion.

This is a bipolar device and has a 175-ns access time. Current is 90 mA from the single +5-V supply.

This is a scanning keyboard encoder that samples 88 keys and provides a parallel ASCII output with parity. Two-key rollover is inherent in the circuit.

For normal operation, +5-V and -12-V supplies are provided as shown. The left network sets the clock to a 50-kHz frequency. The right network sets the debounce time to approximately 8 ms.

Keys are continuously scanned till a closed key routes a matrix output to a sense input. At that time, the scanning stops and the ASCII code, modified by the SHIFT and CTRL keys, is output.

Uppercase-only or uppercase plus lowercase coding may be selected as shown. The output code can be inverted by making pin 20 positive. The parity sense can be changed by making pin 6 positive.

Note that a random and constantly changing output code is provided between key closures. Only when a key is pressed does a stable output result. Circuits downstream from the encoder must ignore the output code between valid keypressed times.

Note further that a shorted key or a short on the key matrix will stop scanning and make the chip look defective. If pin 16 is positive, the chip thinks a key is pressed and will output the code for that key.

A space during clear output can be obtained by shorting X2 to Y8 during the clearing time. This clear should be latched or otherwise held as long as needed to guarantee system clearing.

Typical power-supply current is 5 mA from each supply. Each output will drive one TTL load.

3600

pressed at all times. Uppercase only or lowercase plus uppercase can be selected as shown. Two-key rollover is provided unless diodes are added to the keys. With diodes, n-key rollover results.

Pin 4 is an optional, "any key down" output.

A space during clear output can be obtained by shorting X3 to Y3. The space output will be held till any new key is pressed.

Typical power-supply current is 8 mA from each supply. Each output will drive one TTL load.

#### 26510 QUAD BIDIRECTIONAL BUS TRANSCEIVER T/R 1=SEND 0=RECEIVE +5 V O 3 ī Ŧ R $\overline{R}$ в R 15 (II) 16 14 1 13 12 (10) 0 TOP VIEW B=BUS R=RECEIVE T=TRANSMIT 3 6 8 R R R B 2

The 26S10 contains four transceiver circuits that let you get data on to or off of a bidirectional data bus. The circuit has a very high bus drive capability and provides good noise immunity.

To send, make the T/R input on pin 12 high. Data input on any T input will be inverted and will drive the respective bus output. This data will also appear noninverted at the  $\overline{R}$  output.

To receive, make the T/R input on pin 12 low. Data input will be ignored, and the state of the bus, driven from another source, will appear on the  $\overline{R}$  output. Note that both the transmitted and received data are inverted by this circuit.

Input current to the T/R or any T input is 0.5 mA and is CMOS or TTL compatible. Output drive current from a  $\overline{R}$  output is 20 mA in the low state and 1 mA in the high state. This output can drive at least 10 TTL loads or any number of CMOS loads.

The bus output can source or sink up to 200 mA, and terminating resistors on the bus can be as low as 100 ohms. Receiver switching takes place at 2 V.

Power-supply current is 45 mA from a +5-V supply. All switching times are under 15 ns.

On any bus system, be certain to enable only one transmitter at a time. Note that signals are inverted going on to and off of the bus. Both package grounds must be used.

1488

## QUAD RS232 DRIVER

This package converts input TTL logic levels into bipolar voltages suitable for driving an RS232-C interface. There are four separate drivers. One has a single input. The others have dual NAND inputs.

A digital logic 0 at the input is inverted to a 1 and converted to a +9-V line voltage. A digital logic 1 at the input is inverted to a 0 and converted to a -9-V line voltage.

The inputs are TTL compatible and need 1.6 mA of input current in the low state. CMOS logic having this much output sinking current may also be used.

A capacitor of not less than 330 pF must be placed on each output to limit the slew rate to values within the RS232 spec.

Series power diodes on both supply lines are recommended for failsafe operation.

Power-supply current from each supply is 20 mA.

## 1489

## **QUAD R5232 RECEIVER**

This package converts four separate bipolar RS232-C input logic swings into TTL logic levels. Each of the four separate receivers inverts its logic sense.

On any single receiver, a negative input voltage greater than -3 V will be read as a logic 1. A positive input voltage greater than +3 V will be read as a logic 0.

The capacitors may be used to minimize impulse noise. A value of at least 330 pF is normally used. Resistive connection of this terminal to an external power supply can also be used to shift the trip points and hysteresis of the receiver.

The output can drive up to 10 TTL loads and any number of CMOS loads.

Power-supply current is 25 mA.

#### 75107 DUAL BALANCED-LINE RECEIVER TERMINATING RESISTORS (AT PHYSICAL END OF LINE) 50.0 50 O LINE 2 OUT ENABLE NC 2 14 10 8 13 12 9 TOP VIEW Δ 6 OUT BOTH ENABLE LINE 1 $\mathcal{M}$ TERMINATING RESISTORS **50** Ω

This IC accepts balanced currents from a twisted-pair transmission line and converts them into output TTL logic swings. There are two separate receivers in the package.

For normal operation, pins 5, 6, and 8 are made positive. If the line connected to pin 1 is sourcing current and the line connected to pin 2 is sinking current, a logic 1 will appear at pin 4. If the reverse is true, a logic 0 will appear at pin 4.

Similarly, a sourcing current on 12 and a sinking current on 11 will produce a logic 1 at pin 9 and vice versa.

Grounding pin 6 tri-state disables both outputs, reverting them to a high impedance. Selectively grounding pin 5 disables output 1, and selectively grounding pin 8 disables output 2.

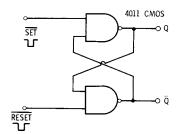

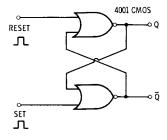

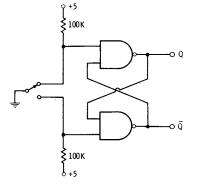

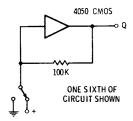

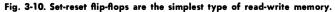

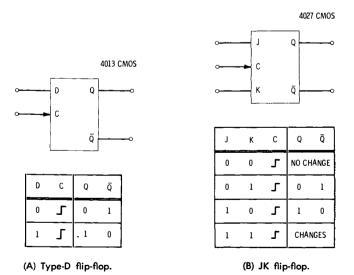

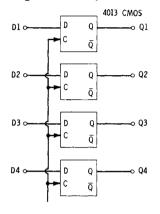

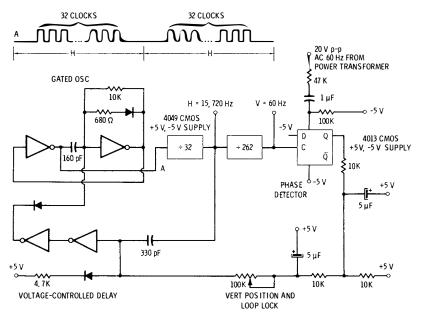

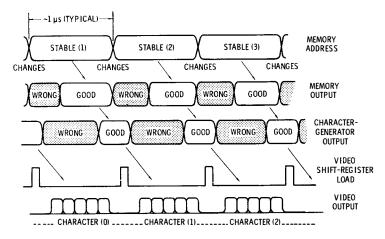

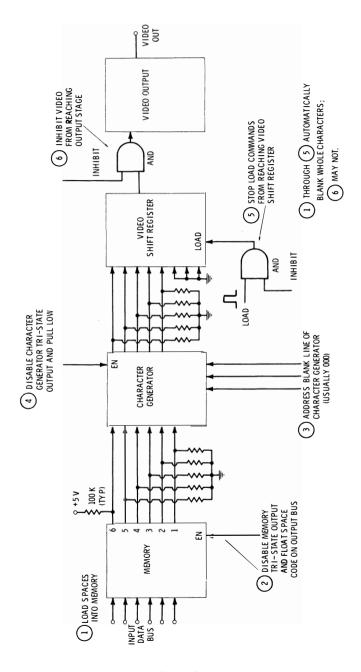

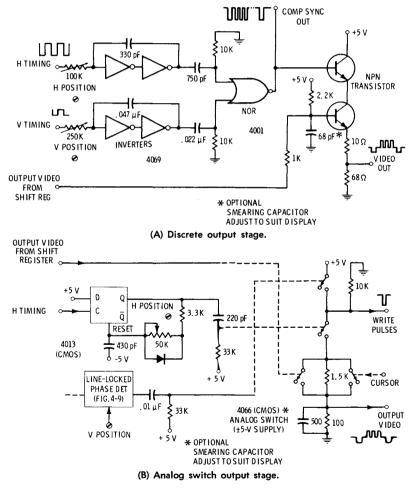

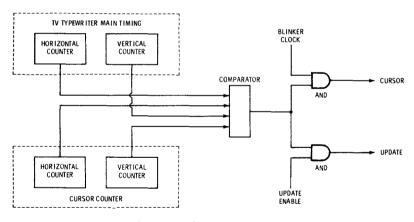

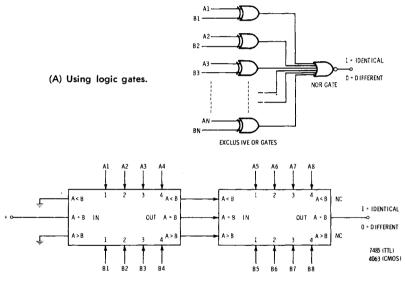

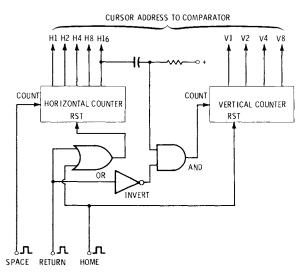

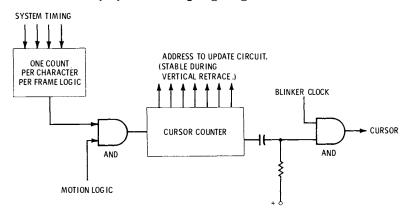

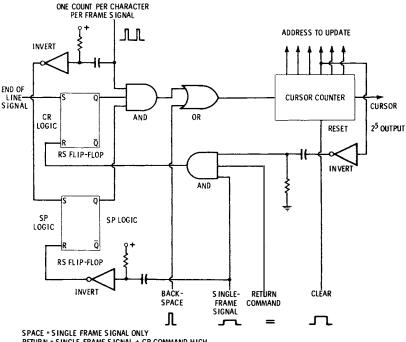

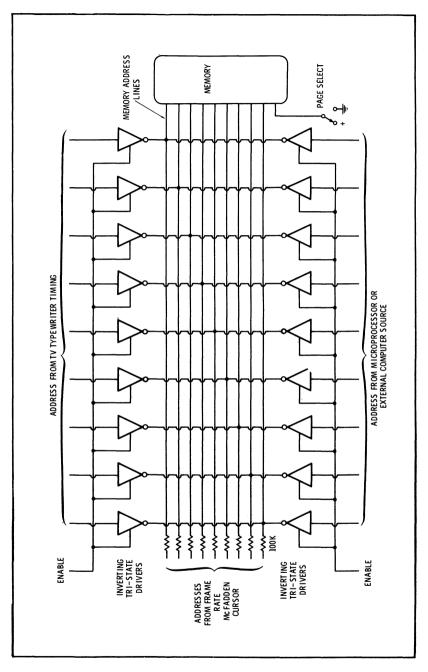

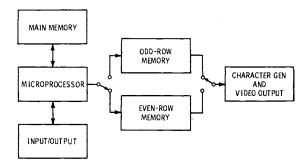

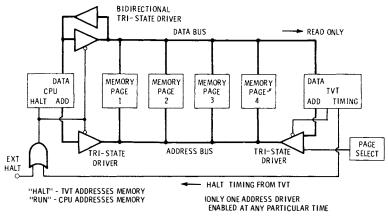

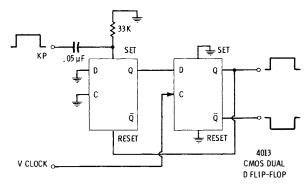

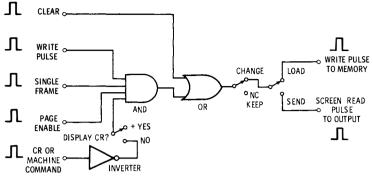

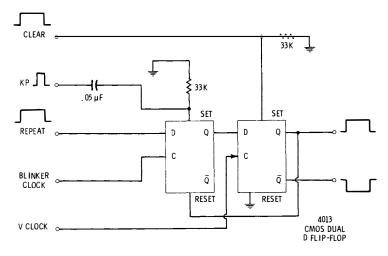

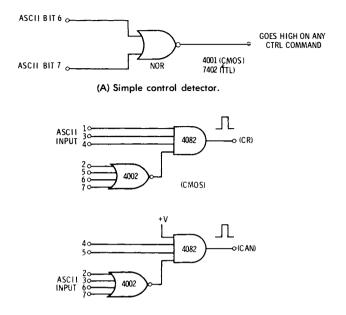

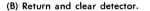

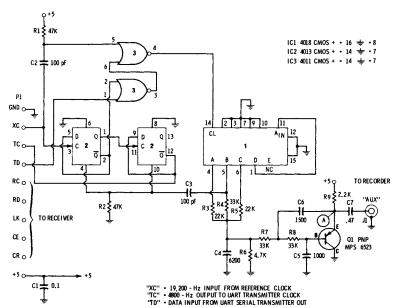

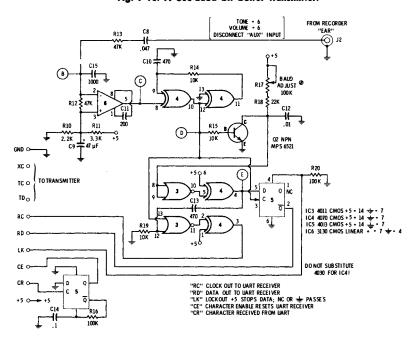

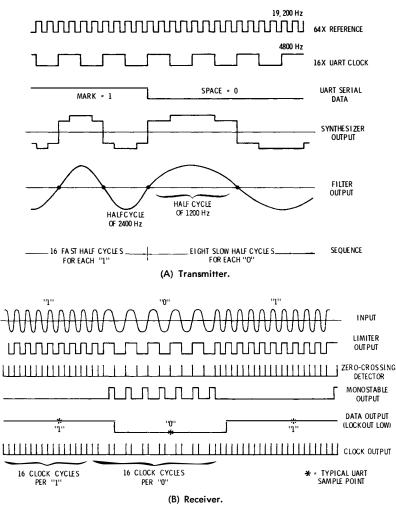

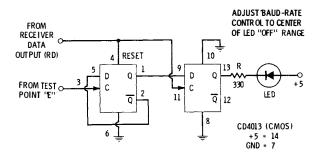

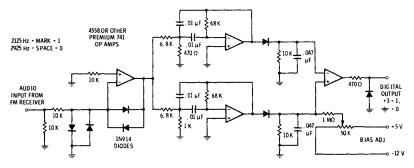

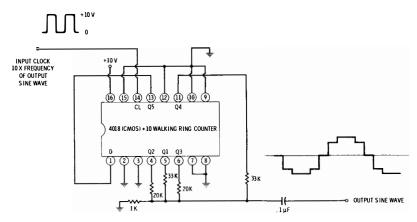

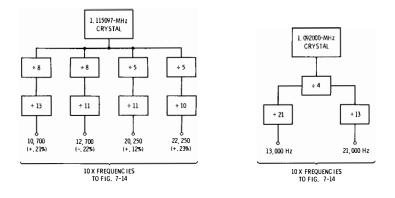

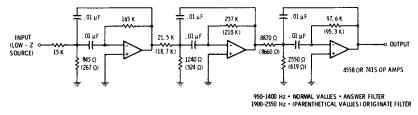

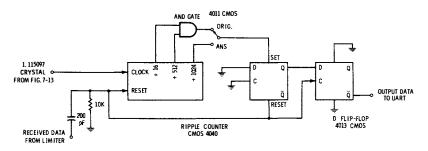

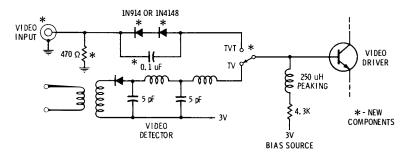

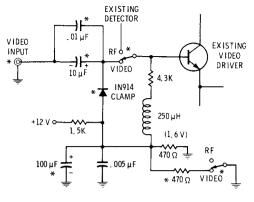

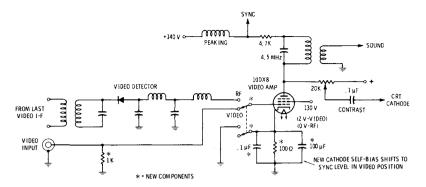

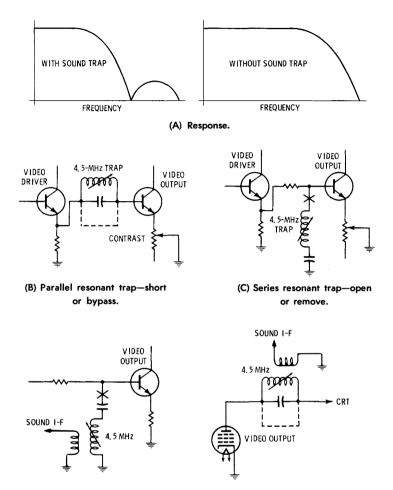

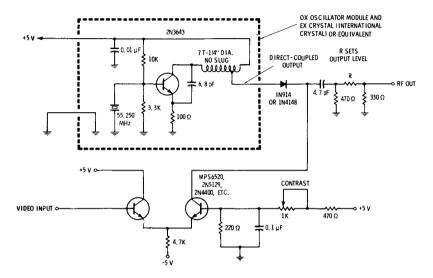

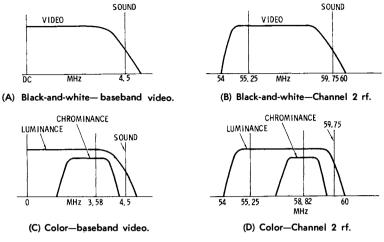

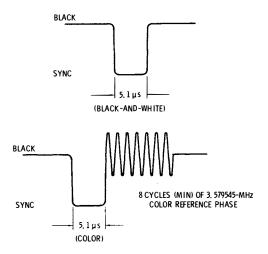

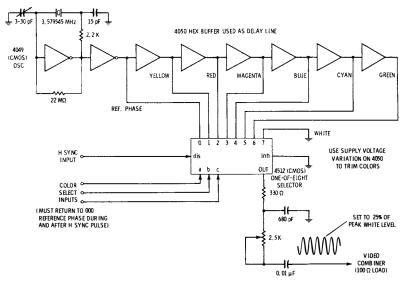

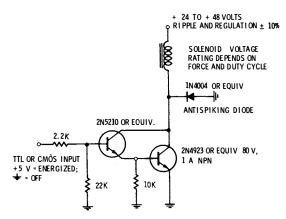

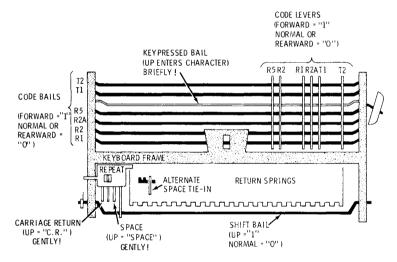

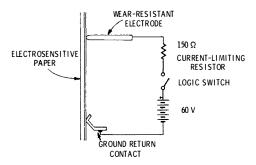

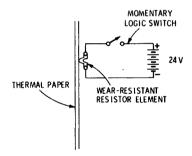

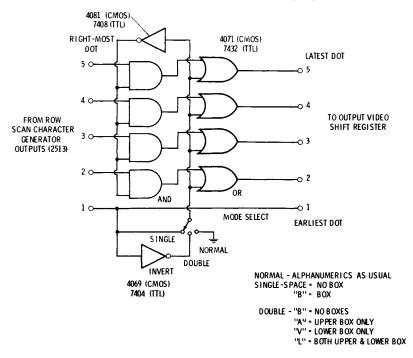

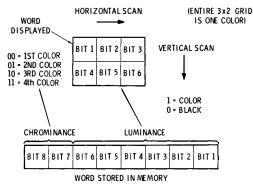

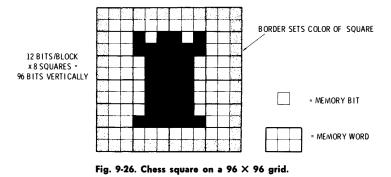

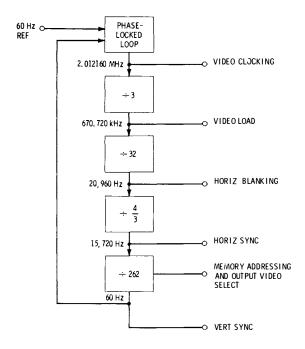

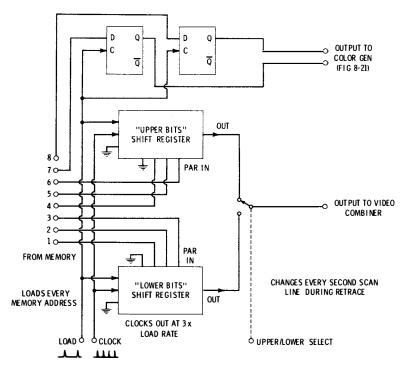

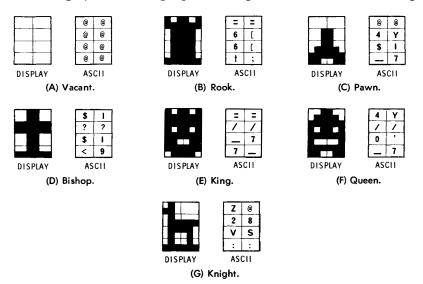

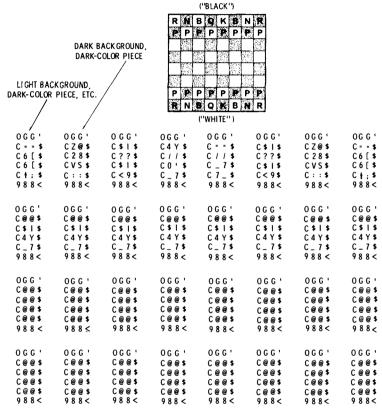

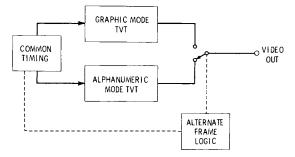

The outputs can drive up to 10 TTL loads. They may drive any number of CMOS loads if a 2.2K pull-up resistor is provided.