# Cookbook

### BY DON LANCASTER

A complete guide to the understanding and using of Resistor-Transistor Logic (RTL) digital integrated circuits.

## RTL Cookbook

by

**Don Lancaster**

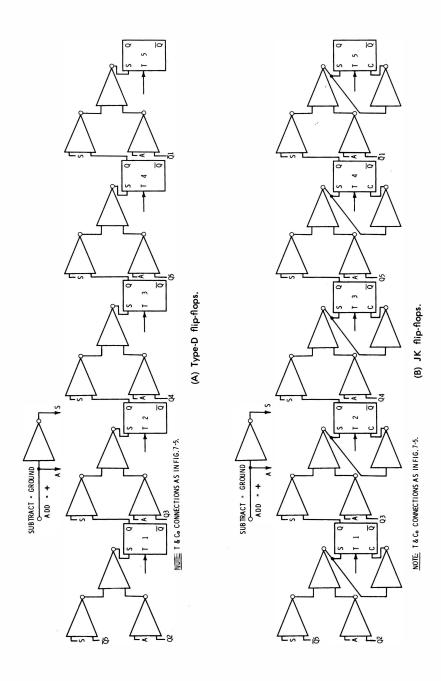

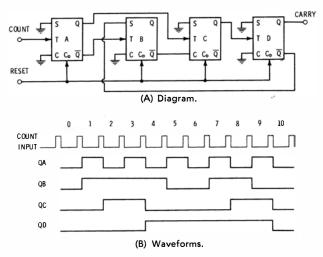

## SYNERGETICS **SP** PRESS

3860 West First Street, Thatcher, AZ 85552 USA (928) 428-4073 http://www.tinaja.com Copyright © 2010 by Synergetics Press Thatcher, Arizona 95552

THIRD EDITION FIRST PRINTING-2010

All rights reserved. Reproduction or use, without express permission of editorial or pictorial content, in any manner, is prohibited. No patent liability is assumed with respect to the use of the information contained herein. While every precaution has been taken in the preparation of this book, the publisher assumes no responsibility for errors or omissions. Neither is any liability assumed for damages resulting from the use of the information contained herein.

International Standard Book Number: 1-882193-10-3

Created in the United States of America.

## Preface

This book will help the electronics experimenter understand and use the low-cost digital integrated circuits now available for practical, everyday electronics projects. The material presented attempts to shatter the myth that digital IC's are too expensive, too complex, or too awesome to use intelligently in simple circuits.

In addition, this book shows the technician the why of digital IC's—how they work, how to use them, and how to design with them. It tells how digital instruments work and how to design and build your own fully integrated IC systems.

Also, this book should be valuable to the engineer who is tired of wading through a stack of application notes and pre-IC computer books to try to find realistic and reasonable designs for such things as divide-by-n scalers, low-cost decimal counter/readouts, IC monostables, synchronizers, or other circuits. The three chapters on counting flip-flops, divide-by-n counting, and decimal counting provide circuits virtually ready to drop into systems for immediate use.

The reasons this book deals entirely with Resistor-Transistor Logic (RTL) are the relatively low prices of this digital-IC line, the ease with which it can be understood, and the ease with which it can be interfaced with conventional transistor circuitry.

The book is organized into two parts, with Chapters 1 through 4 covering the more basic aspects of RTL, and Chapters 5 through 8 dealing with the more exotic RTL applications. Chapter 1 contains elementary nomenclature, and discusses power-supply considerations, mounting, construction practices, etc. Chapter 2 has to do with logic, decoders, logic functions, and the methods of coupling RTL to the outside world. Chapter 3 is on multivibrators; it tells how to build square-wave generators, pulse shapers, astables, monostables, and bistables. The next chapter concerns biasing RTL gates into their amplifying region and building such things as crystal oscillators, operational amplifiers, dc instrument amplifiers, and comparators. This chapter includes "instant-design" charts for speedy amplifier specification. Duty-cycle integration techniques, useful in tachometers and frequency discriminators, are covered in this chapter, also.

Chapter 5 has to do with the JK and Type-D flip-flops, the eight basic JK flip-flop configurations, and some counter techniques. Here, we also look at the input and output restrictions on counting flip-flops, and investigate the techniques essential for reliable and predictable operation. Chapter 6 is on divide-by-n counting and scaling—how to build reliable, frequency-independent, low-cost dividers, decoders, counters, and steppers for any desired count. Decimal counters are given thorough coverage in Chapter 7. The final chapter is on digital instruments. It shows how to tie together the circuits in the rest of the book to build frequency counters, digital voltmeters, electronic stop watches, and other complete digital systems.

I wish to extend my thanks to Billy G. Wood and Rudy O. Nonnenmann for their technical and proofing assistance in putting this book together.

DON LANCASTER

#### Addendum

It is rare for any technical book written in 1968 to still be in demand—especially a book on integrated circuits. Apparently, we have a classic of sorts on our hands. Your response to this book so far has generated the continuing series of Cookbooks—RTL, TTL, Active Filters, TV Typewriter, CMOS, and the related Users Guide to TTL.

Much of the information in this book is now out of date. While you can still buy and use RTL, bigger and better logic families are now available. (Check into CMOS in particular.) More critically, the problems and thought processes involved when you are working with digital IC's have matured and changed dramatically. We simply don't worry about the same things anymore.

Rather than try to update this text, we've purposely left things as they were. If for no other reason, this leaves us with an untampered historical record of the thought processes and concepts involved with early pre-MSI digital integrated circuit work.

Thanks again for your interest and support of this continuing series.

DON LANCASTER September 1975

## Contents

#### CHAPTER 1

| Some Basics                                                                                                                                                                                                                                                                                                                                   | 7 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Types of Logic Gates—Two-Input RTL Digital-Logic Gate—Other<br>Logic Blocks—Multiple-Function IC's—Power Levels—Loading:<br>Fan-In and Fan-Out—Packages and Lead Conventions—Mounting<br>Techniques—Tools—Soldering—Power Requirements—Current<br>Requirements—Battery Operation—Line Operation—"Bad" and<br>"Burned-Out" Integrated Circuits |   |

|                                                                                                                                                                                                                                                                                                                                               |   |

#### CHAPTER 2

The Two-Input Gate as a Simple Switch—Computer Logic—Ones and Zeros—The NOT Circuit—Two-Input Logic Functions—Multiple-Input Logic—Building Logic Functions With RTL—Choosing Logic Definitions—What Good Is Logic?—Decimal-to-Binary Encoder—Binary-to-Decimal Decoder—Indicating States: Driving the Outside World With RTL

#### **CHAPTER 3**

| MULTIVIBRATORS | •••••••••••••••••••••••••••••••••••••••             | 49 |

|----------------|-----------------------------------------------------|----|

| Two Inverters  | Back-to-Back—Triggering: the Bistable Multivibrator |    |

10

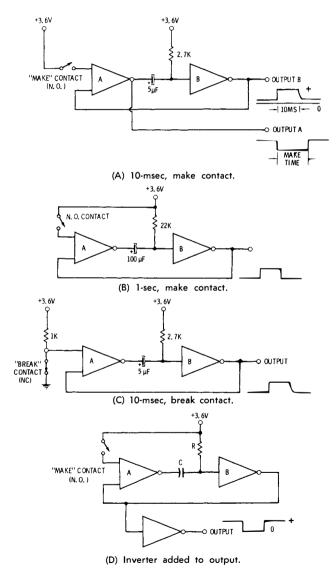

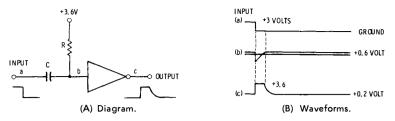

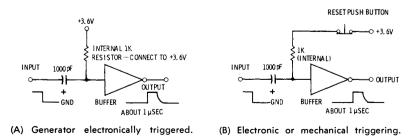

-Loading—The Reset-Set Flip-Flop—Triggering Restrictions on the RS Flip-Flop—Counting With RS Flip-Flops—The Monostable Multivibrator—Contact Conditioners—The Half Monostable—The Astable Multivibrator—Other Multivibrator-Type Circuits

#### CHAPTER 4

####

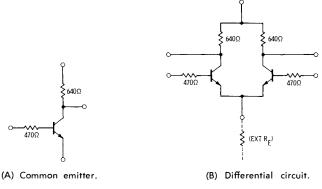

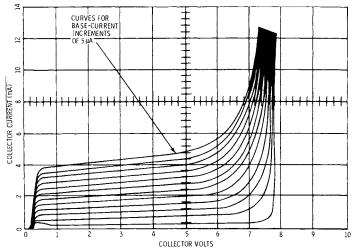

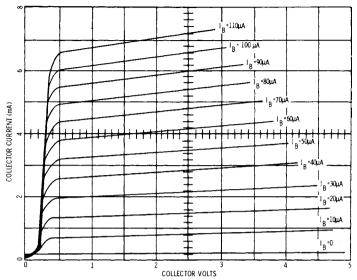

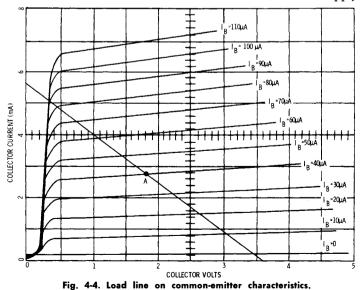

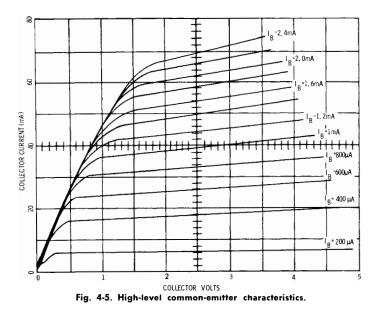

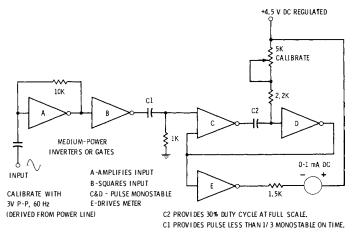

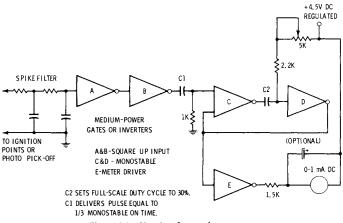

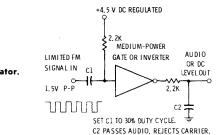

RTL Gates as Linear Amplifiers—Characteristic Curves—High-Power Operation—Class-A Common-Emitter Amplifier Without Feedback—Class-A Common-Emitter Amplifier With Feedback— Differential Amplifiers—Restrictions on the Differential Amplifier —Linear Applications for RTL—Some Typical RTL Linear Circuits —Differential-Amplifier Applications—Comparators—Duty-Cycle Integrators

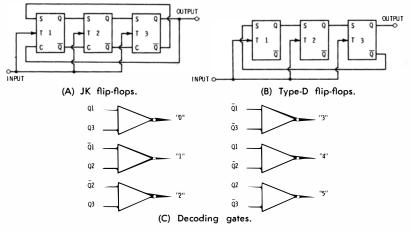

#### CHAPTER 5

| Counting Flip-Flops                                        | 105 |

|------------------------------------------------------------|-----|

| The JK Flip-Flop—Using JK Flip-Flops—The Type-D Flip-Flop— |     |

Using the Type-D Flip-Flop

#### **CHAPTER 6**

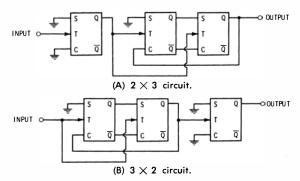

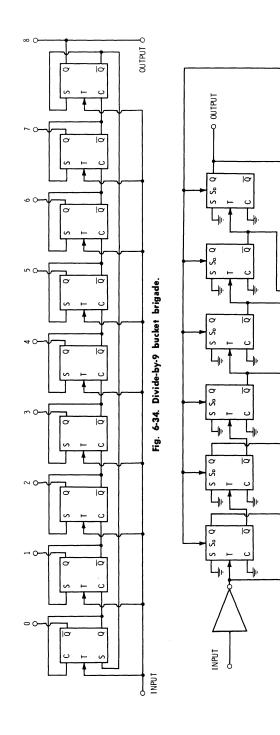

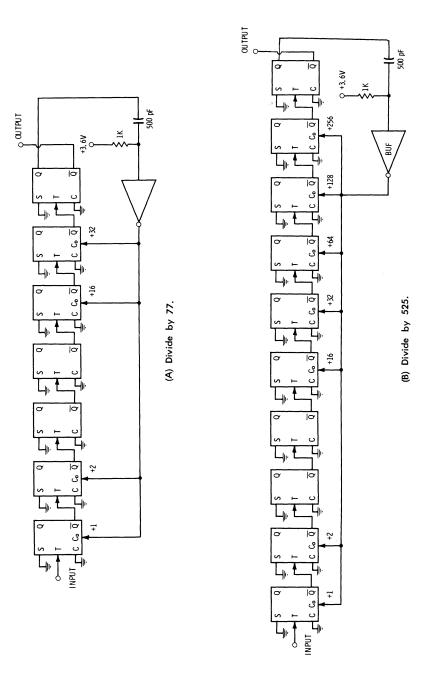

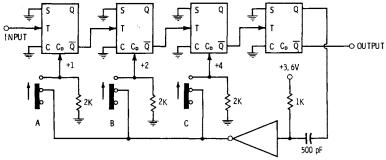

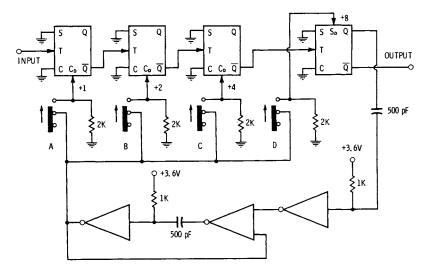

| Scaling and Divide-by-n Counting                                                                          | 133 |

|-----------------------------------------------------------------------------------------------------------|-----|

| Counter Qualities—Design Pitfalls—Low-Modulo Counters—High-<br>Modulo Counters—Fractional-Modulo Counters |     |

#### **CHAPTER 7**

| DECIMAL CO | UNTING | • • • • • • • • • • | ••••• | 171 |

|------------|--------|---------------------|-------|-----|

|            |        |                     |       |     |

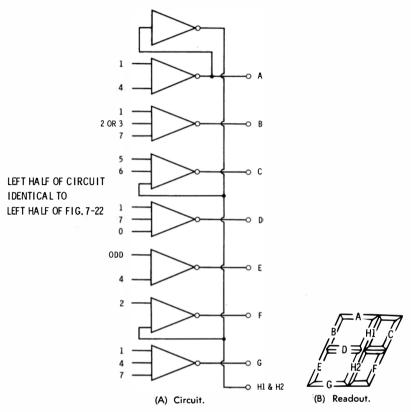

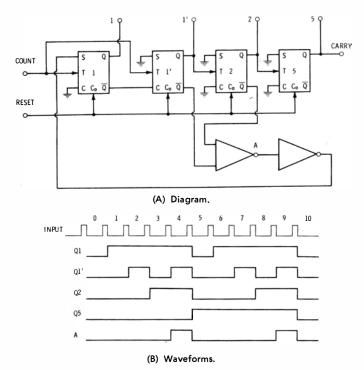

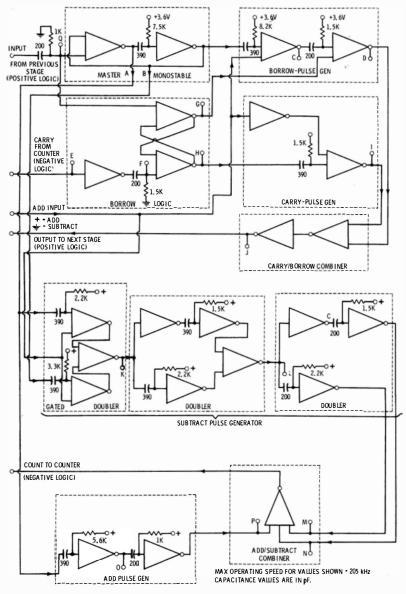

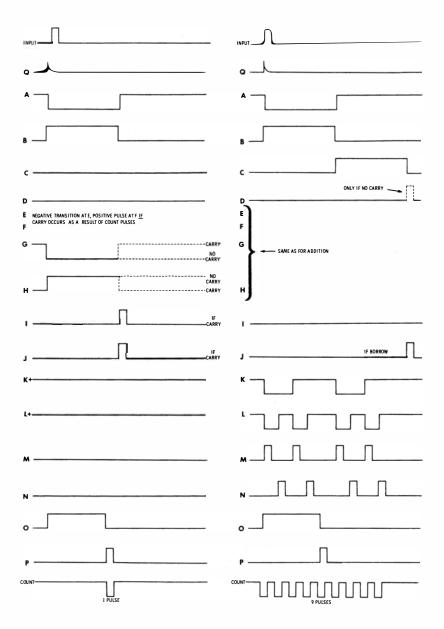

Decimal Counter Applications—Some Practical Decimal Counters— A 9's Complement Up-Down Counter

#### **CHAPTER 8**

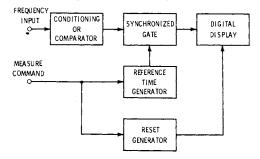

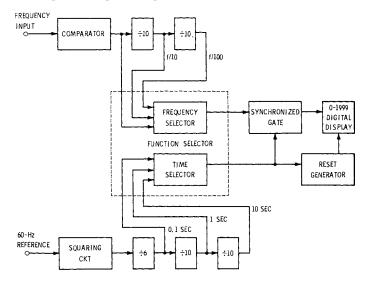

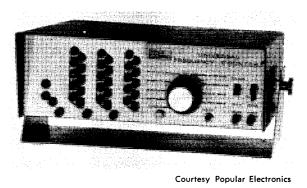

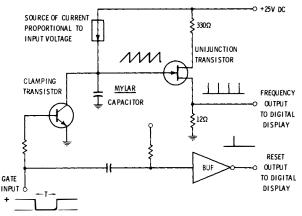

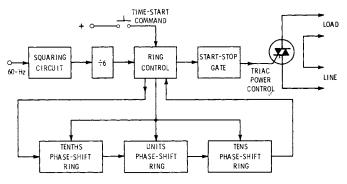

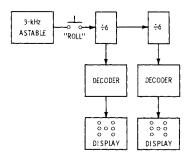

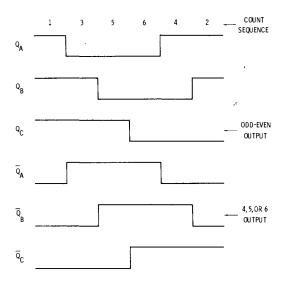

DIGITAL INSTRUMENTS AND OTHER RTL APPLICATIONS ...... 203

Digital Instruments—Speed-Accuracy Product—Composite Digital Instruments—Some Relatively Complex RTL Applications—Some Simple RTL Applications

## CHAPTER 1

## Some Basics

A logic gate is any device that obeys certain predetermined rules to turn an output off or on upon some coincidence of signals at its input. A kitchen-sink faucet is a logic gate—it provides an output if either the hot or cold input is provided with an on signal. This is an example of an "OR" gate. A garden hose is an "AND" logic gate, because both the outdoor faucet and the nozzle valve must be provided with an on command in order for the output to be turned on.

A digital logic gate is a logic gate whose inputs and outputs represent only a "yes" or a "no" command. (That is, either there is a voltage or there is not; things are either on or they are off—there is no halfway condition.) While a digital water source would hardly be useful, there are many advantages to digital logic. Simple elements are called for; they need only remember a "yes" or a "no." And, with enough serial combinations of yes and no outputs, practically any event or number can be represented. The right combinations of digital logic gates, along with some other slightly more complicated logic blocks, make it possible to build anything from an electronic dice game to a television pattern generator.

#### TYPES OF LOGIC GATES

There are many forms of logic gates. They may be mechanical, hydraulic, chemical, pneumatic, optical, electromechanical, or electronic. The electronic logic is by far the most prevalent, because of the great number of gates in use by the computer industry. Integrated circuits (IC's) were called upon about a decade ago to reduce the size, cost, and power consumption of electronic computer gates. As a result, there are many different forms of integrated-circuit digital-logic gates available today. Each of these forms is called a *logic family*, and is usually identified by three letters, such

as RTL, DTL, ECL, MOS, TTL, etc. There are many considerations that enter into the choice of logic family for a given application. These factors include cost, speed, complexity, availability, noise immunity, interfacing, and a dozen other more subtle considerations. An integrated-circuit logic family called RTL, short for Resistor Transistor Logic, has characteristics that make it suitable for experimental work and applications ranging from simple projects through digital instruments and complex systems.

The advantages of RTL integrated circuits include relatively low price and good availability. Many of these IC's cost less than \$1.25, and since most of them are multifunction devices which include several digital logic gates or other logic blocks in one package, the per-function cost can be even lower. RTL is easy to interface with conventional npn transistor circuits, and in many cases it lends itself to *replacement* of conventional circuitry. This is particularly true of the circuits in Chapter 4. Another advantage is that RTL is easy to understand.

Compared to other logic families, RTL is relatively "slow"; it may be used only at speeds less than 10 million counts per second. It is somewhat noisy, requires considerable supply power, and is limited in drive capability. While these limitations are severe to the large-scale computer designer, they tend to be of negligible importance in simple circuits containing only a few IC's. With RTL, the total price usually is less than the cost of doing the same job (and often a poorer one) with conventional transistors.

#### TWO-INPUT RTL DIGITAL-LOGIC GATE

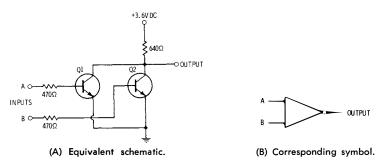

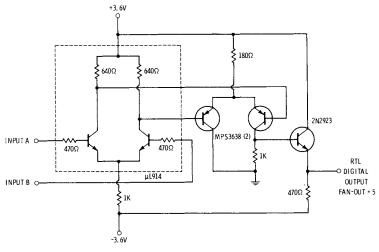

The work horse of the RTL logic line is the two-input gate. This gate and its logic symbol are shown in Fig. 1-1. (Throughout this book, we will be using a "shorthand" form of logic symbols in which the symbol for a two-input gate is the same anywhere this particular circuit is used.) Fig. 1-1 shows three resistors and two transistors. The transistors are npn and behave exactly like ordinary silicon transistors. This gate is operated, or *conditioned*, by either applying positive voltage to the inputs or grounding

Fig. 1-1. Two-input RTL gate.

them. The gate responds by providing either a positive or a grounded output.

RTL is a *saturated* logic family. That is, all the internal transistors are either completely off or conducting the maximum possible current (except for the brief interval during which they switch between these two states). Everything is always either on or off.

If *botb* inputs to the two-input gate are grounded, neither base receives current, and both transistors remain off. Since both transistors are off, there is no collector current through either transistor, and thus there can be no current through the 640-ohm collector resistor. There can be no voltage drop across this resistor if there is no current through it, and the output terminal is therefore positive.

If a positive voltage is applied to input A, transistor Q1 saturates (turns on) and draws the maximum possible current through the 640-ohm collector resistor. The entire supply voltage (less a 0.2-volt saturation drop) appears across this resistor, and the output terminal is effectively grounded. The same thing would happen if a positive voltage were applied to terminal B, except that Q2 would saturate and ground the output. If both A and B are made positive, the output still is grounded. To make the output *positive, both* inputs must be *grounded*. To *ground* the output, *either* or *both* inputs must be made *positive*.

The two-input gate is used to perform *decision logic* based on the absence or coincidence of input signals. The output from one two-input gate may drive several others directly. If two two-input gates are combined back-to-back, a circuit called a multivibrator is produced; it can be made to have a memory, generate pulses, or oscillate, depending on just how the gates are connected. Further, this particular type of RTL two-input gate can be biased into its class-A region and used in low-cost crystal oscillators, input amplifiers, operational amplifiers, and comparators. Thus, the twoinput gate can be made to serve many purposes in the digital-IC world.

#### **OTHER LOGIC BLOCKS**

While the two-input gate is the most versatile and widely used RTL digital logic block, there are other available logic blocks which are normally used in combination to produce desired circuit functions with a minimum number of parts. Actually, we could use nothing but two-input gates in any digital circuit, but most circuits would be far more complicated. We now turn to these other RTL logic blocks to see how they function.

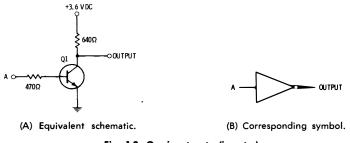

#### Inverters

A one-input gate (Fig. 1-2) is called an *inverter*, or a NOT gate. If the input is made *positive*, Q1 receives base current, and the output goes to ground. If the input is grounded, the output goes positive. A positive voltage and a grounded condition are opposites in digital logic. We *must* have

one or the other at any logic terminal at any time. These opposites are called *complements*; the complement of a grounded terminal is a positive terminal, and vice versa.

A logic signal is called either a "1" or a "0." A 0 is a complement of a 1. The 0 is not necessarily associated with the grounded-terminal condition; in fact, 0 usually is associated with the *positive* terminal condition, as will be shown later.

An inverter is a useful device for generating the complement of a logic signal, since it automatically produces a 0 if a 1 appears at the input, and a 1 if a 0 appears at the input. An inverter also makes it possible to change the *meaning*, or the *definition*, of a 1. For certain circuits, we may want a 1 to correspond to the grounded input condition, while other circuits may operate only with a 1 corresponding to the positive input condition.

Fig. 1-2. One-input gate (inverter).

Inverters may be used back-to-back in pairs to form a latch or a memory. They may be combined with a capacitor to form a simple pulse shaper, time delay, or oscillator. They also may be biased in their class-A region for operation as a low-level amplifier or a crystal oscillator.

#### **Gates With More Than Two Inputs**

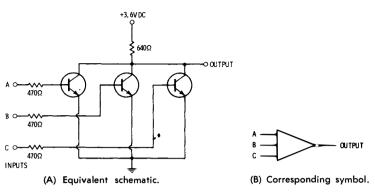

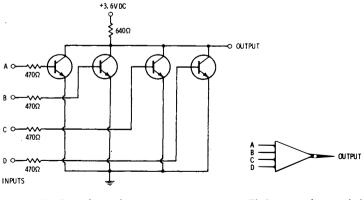

Sometimes we want a circuit to respond logically to a coincidence or absence of more than two inputs. In these cases, we can use a three-input gate, a four-input gate, or any gate with a gate expander attached to provide the necessary number of inputs. The three-input gate is shown in Fig. 1-3. This circuit has three transistors and four resistors, and its operation is just like that of the inverter and the two-input gate. When any input is positive, the corresponding transistor is saturated, and the output is grounded. When all inputs are grounded, the output swings positive.

As with the two-input gate and the inverter, the three-input gate *inverts* the logic, and produces a complementary output. Positive at the input provides ground at the output.

Adding one more resistor and transistor to the three-input gate makes a four-input gate (Fig. 1-4). Here, the output is grounded if any of the four inputs receives base current, and positive only if all four inputs do

Fig. 1-3. Three-input RTL gate.

not receive base current. The four-input gate is used exactly as the two- or three-input gate is used, except, of course, that it responds to the logic signals present on all four inputs.

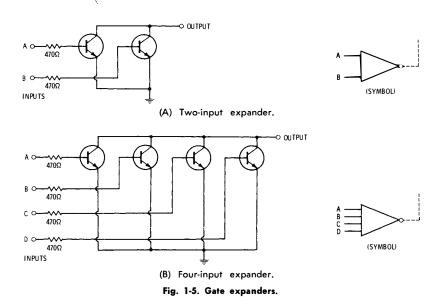

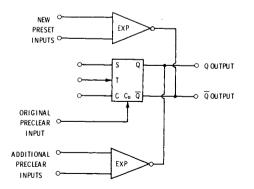

Whenever more than four inputs are needed on a logic gate, a gate expander is necessary. This is an IC that provides enough extra input transistors to bring a gate to the desired number of inputs. Two gate expanders are shown in Fig. 1-5 along with their logic symbols. One, two- and four-input gate expanders are readily available. Fig. 1-6 shows how a four-input gate expander may be used with a four-input gate to produce an eight-input gate.

Gate expanders may be doubled up as required to obtain any reasonable number of logic inputs. They are useful when conventional circuitry is interfaced with IC's, and they also may be used to add extra "preclear" and "preset" inputs to certain flip-flops which will be discussed later.

(A) Equivalent schematic.

(B) Corresponding symbol.

Fig. 1-4. Four-input RTL gate.

A four-input gate may be converted into a three-input gate by grounding one input, into a two-input gate by grounding two inputs, and into a one-input gate (inverter) by grounding three inputs. Since several gates are usually available in each IC package, the total number of IC packages needed to do a job often can be reduced. In any RTL circuit, *all unused gate inputs should always be grounded*. Failure to do so can lead to noise problems and erratic operation.

It is also possible to tie two-input gates together at their outputs to produce a single four-input gate, or to use two three-input gates to make a six-input gate. Since this connection alters both the input drive requirements and the output drive availability (it puts both collector resistors in parallel), it should be used with discretion. Connecting more than two gates together at their outputs is not recommended.

Sometimes the effect of another gate input may be gained by selectively applying supply voltage to the entire IC package. This technique is called *strobing* and, in special cases, can produce the effect of an additional gate input on each gate in the IC package.

Fig. 1-6. Use of a gate expander.

Fig. 1-7. One-input inverting buffer.

#### **Buffers**

A *buffer* is a higher-power IC used whenever many other IC's have to be driven from a single source, or whenever a more powerful output signal is needed to drive external circuitry.

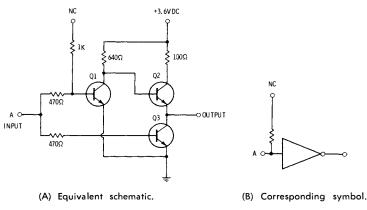

There are several types of buffers. The simplest and most common have one input and invert the signal; thus they are nothing but high-power NOT gates, or inverters. This type of buffer is shown in Fig. 1-7. If the input is grounded, Q1 and Q3 remain off. Transistor Q2 then receives base current through the 640-ohm resistor, and the output terminal swings positive. If the input is made positive, base current reaches Q1 and Q3, and Q3 turns on, grounding the output. Since Q1 is on, Q2 receives no base current and stays off. The output stage actually operates in a push-push manner, forcing the output terminal to either a positive voltage or ground, following the commands of an input signal.

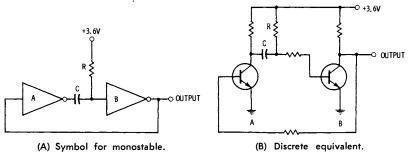

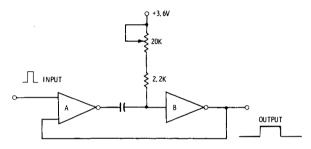

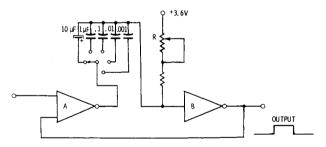

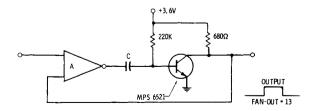

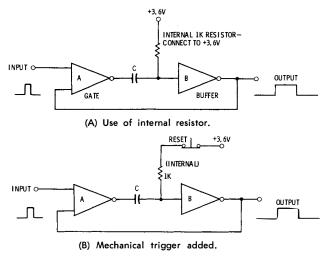

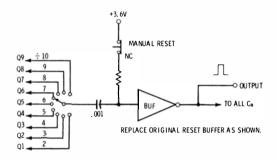

The 1k resistor shown is internal to the buffer and is brought out to a separate pin; this resistor is normally left unconnected. In Chapter 3 it will be shown that by connecting this resistor to the positive voltage source and by capacitor-coupling the input, the buffer may be made into a relatively high-power pulse generator, useful for waveform shaping and generating reset pulses in IC systems.

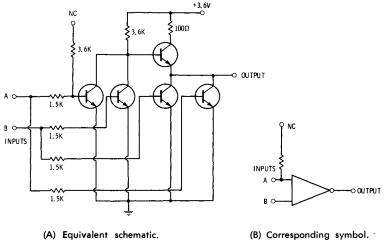

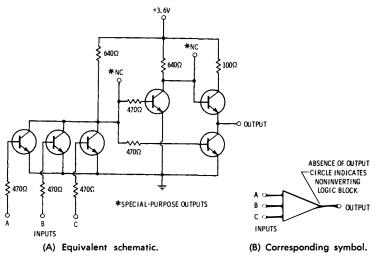

There are fancier forms of buffers that have more than one input. These allow input logic to be performed as well as providing a high-power output. A two-input inverting buffer and a three-input noninverting buffer are examples of these fancier logic blocks. They appear in Figs. 1-8 and 1-9, respectively.

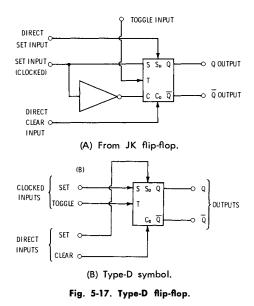

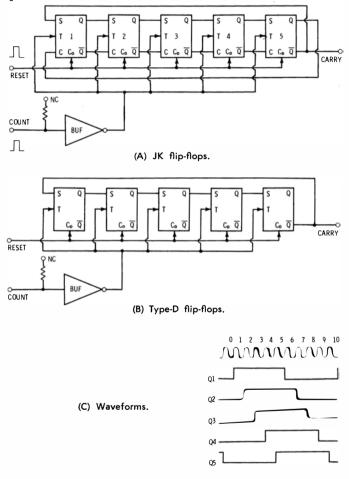

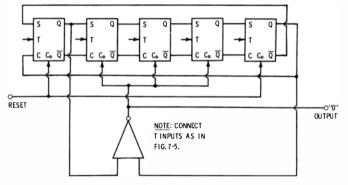

#### **JK Flip-Flop**

The JK flip-flop is a more complex IC logic block and is useful for performing binary division, storage, counting, scaling, and other more com-

Fig. 1-8. Two-input buffer.

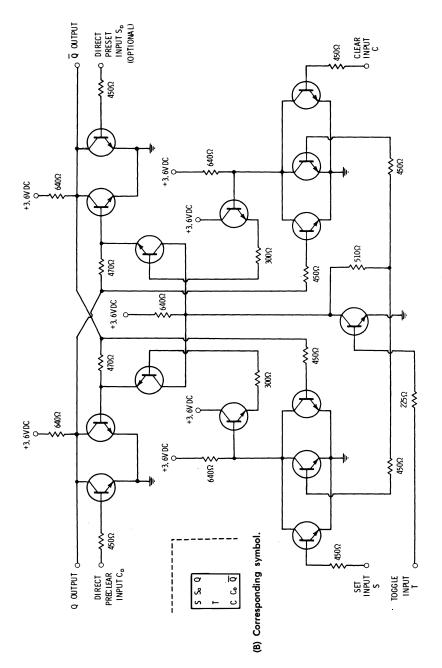

plex forms of logic. It can divide by two without the need for other logic elements. JK flip-flops have four and sometimes five inputs, called the *set*, *toggle*, *clear*, *preclear*, and *preset* inputs, and two complementary outputs called the "Q" and " $\overline{Q}$ " outputs. The schematic and logic symbol of the JK flip-flop are shown in Fig. 1-10. Details of this particular logic block are contained in Chapter 5.

Fig. 1-9. Three-input noninverting buffer.

Fig. 1-10. JK flip-flop.

(A) One equivalent schematic.

The essential difference between the JK flip-flop and the simpler logic blocks is that a JK flip-flop runs in a *clocked* mode. Regardless of what is done to the set and clear inputs, nothing happens until the instant the signal on the toggle input *abruptly drops* from a positive voltage to ground. We say that the JK is *edge sensitive* to the *negative-going toggle transition*. This circuit action allows us to "set up" what the JK flip-flop is supposed to do *independently* of *when* it actually does it. This feature is particularly useful in shift registers, decimal counters, and other counter circuits.

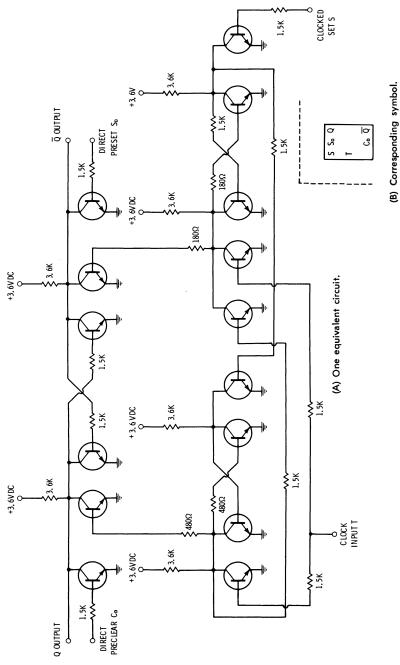

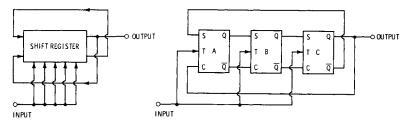

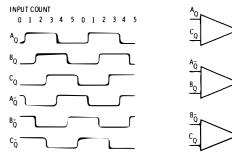

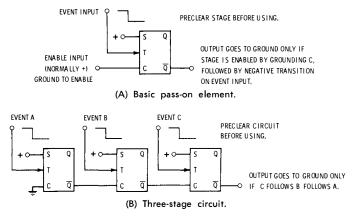

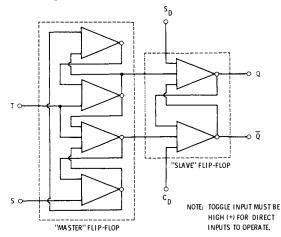

#### **Type-D Flip-Flop**

The Type-D flip-flop is another version of a clocked logic block whose input commands, or *conditioning*, may be set up prior to the actual performance of the logic. Externally, the Type-D flip-flop is very similar to a JK flip-flop, except that it lacks a clear input. It is used primarily for shift registers, arithmetic calculations, and storage circuits. The schematic and logic symbol for the Type-D flip-flop are shown in Fig. 1-11. Details of this device are contained in Chapter 5.

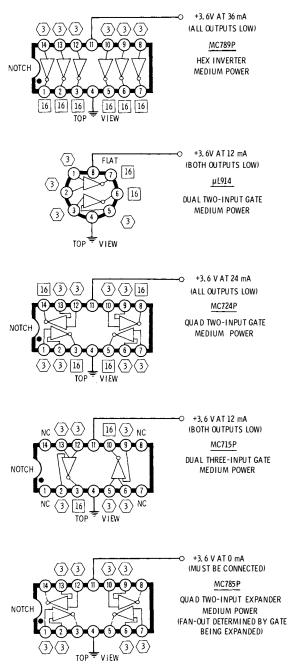

#### **MULTIPLE-FUNCTION IC'S**

Most of the available RTL integrated circuits combine two or more logic blocks in the same package, thus reducing the total number of packages needed for any particular circuit, and making maximum use of all available pins on the IC package. For instance, a dual two-input gate is an IC package with two independent two-input gates in the same package. Similarly, a quad two-input gate contains four independent two-input gates in the same package, and a dual four-input gate has two independent four-input gates in the same package. The only common connections between the gates are the positive source and ground. All the gates in a single IC may be used either together or in totally unrelated circuits. There is no crosstalk problem.

Other popular configurations are dual flip-flops, dual buffers, hex inverters (six to a package), and triple three-input gates. Some special combinations are also available, such as a JK flip-flop, an expander, and two buffers. These are particularly useful for reducing the total number of IC packages used in specialized applications.

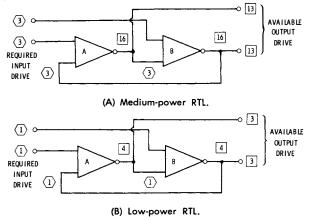

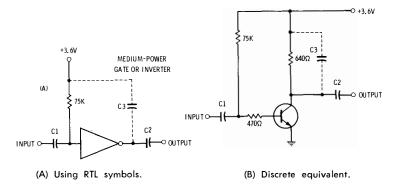

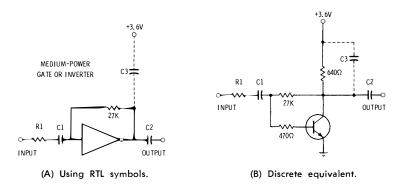

#### **POWER LEVELS**

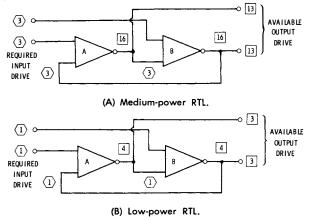

There are currently two types of RTL available, the *medium-power* RTL and the *milliwatt*, or *low-power*, RTL. These two types usually are similar in cost and differ primarily in the internal power dissipation. The internal power consumption is four to five times greater in the medium-power RTL than in the low-power RTL. For instance, the two-input gate of Fig. 1-1 is a medium-power gate. It has a 640-ohm collector resistor and dissipates

Fig. 1-11. Type-D flip-flop.

about 25 milliwatts with both inputs positive. The equivalent low-power-RTL two-input gate has a 3.6k collector resistor and dissipates about 5 milliwatts with both inputs positive.

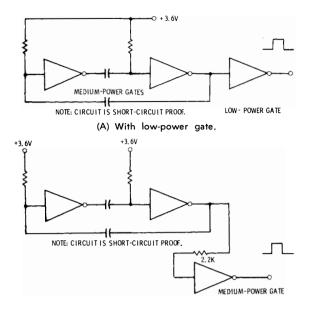

Low-power operation is never obtained free. The low-power IC's have restricted operating speeds and very restricted drive capabilities. Often a circuit made entirely from low-power IC's requires more packages, since extra buffers may be needed to obtain sufficient drive levels. The choice of low-power versus medium-power RTL depends on the complexity of the circuit and the available power supply. The usual choice is to use the medium-power RTL and save the low-power units for use when special design problems occur.

#### LOADING: FAN-IN AND FAN-OUT

All the transistors in the RTL logic blocks operate either in the saturated or cut-off mode; that is, the equivalent transistors are either completely conducting or completely cut off during steady-state operation. It is reasonable to expect that there is some minimum input drive level needed to provide enough base current to keep the input transistors saturated; similarly, there must be a maximum available output current for any IC. The input current requirement is called the *fan-in* of the circuit, and the output drive capability is called the *fan-out* of the circuit.

Rather than worrying about delivering so many milliamperes into a transistor with such-and-such gain, a much simpler method is used in integrated-circuit work. The manufacturer investigates the worst-case performance of his logic line and then assigns a *loading number* to each terminal. A loading number of 3 on an input means that 3 units of drive are *required*. A loading number of 15 on an output means that 15 units of drive are *available*. We can load an output with any combination of units less than or equal to the available output. For instance, one type of JK flip-flop has a fan-out of 10. This output can be used to drive any combination of gates that total 10 units or less. Three medium-power gates would require 3 units of drive each, for a total of 9; we may safely connect these to the 10-unit output. If we added a fourth gate of fan-in 3, we would be trying to get 12 units from an output with a fan-out of 10, and the circuit most likely would not perform properly.

The fan-out for any IC should not be exceeded. This is particularly true of the low-power RTL. The fan-in and fan-out numbers for the low-power and the medium-power RTL are compatible. Thus, a low-power gate with a fan-out of 3 can drive a medium-power gate with a fan-in of 3.

When the available fan-out is not enough, it can be "amplified" by an additional gate, inverter, or buffer. For instance, a low-power gate amplifies a 1 to a 3; a medium-power gate or inverter amplifies a 3 to a 16; a buffer amplifies a 5 to an 80. Buffers are particularly handy whenever several logic devices are to be driven in parallel. As an example, if ten flip-flops are to

Fig. 1-12. RTL integrated-circuit packages.

be reset simultaneously, 30 units of drive are required; if they are to be toggled simultaneously, 50 drive units are needed.

There are two factors that may have to be considered when it is desired to amplify the fan-out. Almost all gates and buffers invert the input and provide its complement at the output. Inversion in the final output can be avoided either by picking an input complementary to the desired one or by reinverting the output. A second possible problem is time delay introduced as the signal goes through a gate or an inverter. While this delay may be as little as 12 nanoseconds (billionths of a second) or so, it may become important in high-speed systems.

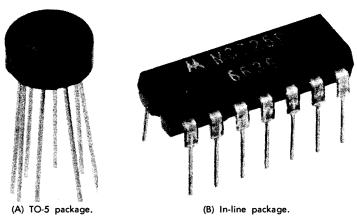

#### PACKAGES AND LEAD CONVENTIONS

Modern integrated circuits come in a wide variety of packages, but the low-cost industrial RTL versions are mostly limited to one of two multilead molded plastic packages, an eight-lead, TO-5 round package and a rectan-

(A) TO-5 package.

(B) In-line package.

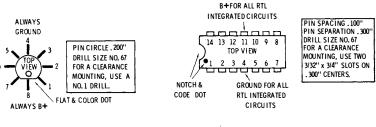

Fig. 1-13. IC pin information.

Fig. 1-14. Some available

**RTL** integrated circuits.

gular dual in-line package with 14 leads. These packages are shown in Fig. 1-12.

Both packages have their leads identified counting counterclockwise from the top, and most manufacturers use this top-view convention because it makes the schematic, layout, and logic diagrams nearly identical. From a practical standpoint, this uniformity simplifies circuit-board layout and troubleshooting.

The TO-5 package has pin 8 identified by a flat, a tab, or sometimes a color dot on the package; the count proceeds counterclockwise around the package when viewed from the top. The dual in-line package is identified by a dot beside pin 1. The count then proceeds down one side and back up the other side, returning to pin 14 directly above pin 1. A code notch between pins 1 and 14 also aids identification. These numbering conventions are shown in Fig. 1-13.

The supply-voltage connections are always the same for a particular package. On the round, eight-lead package, pin 4 is always ground; pin 8 is always B+. The 14-lead rectangular package always has lead 4 grounded and lead 11 connected to B+. This is true of all RTL IC's but is *not* true of other (non-RTL) logic families that may be supplied in the 14-lead rectangular package.

RTL is offered in several lines, differing in temperature performance and tolerance limits. For experimental work, either the hobby/experimental or the "industrial" grade RTL normally is used. These types are relatively low in cost and are the most readily available. They have a specified operating range of +50 to  $+130^{\circ}$ F. Fig. 1-14 gives details on IC's referred to in the circuit descriptions in this book. The integrated circuits of Fig. 1-14 are stocked by a number of electronic distributors.

The prices of IC's vary from unit to unit. The package price might be on the order of from one to three dollars in single quantities, depending on the complexity of the internal circuitry.

Always obtain a complete set of data sheets before you begin any IC work. These sheets serve as a road map of what can and cannot be done with integrated circuits, what their temperature restrictions are, their fan-in and fan-out, their power requirements, and their pin connections.

#### **MOUNTING TECHNIQUES**

There are several practical ways to mount RTL IC's. Those of greatest interest to the technician and the economy-minded experimenter are sockets, standoffs, and PC methods.

#### Sockets

Sockets are handiest when the IC's have to be reused, but they are often expensive, and the close lead spacing often requires some fancy and fine wiring work. Sockets for IC's are usually a distributor stock item, and may vary in price from less than \$1 to \$12 or more each. Usually the more expensive ones are made of Teflon and are intended for miliary use. For simple systems, the cost of sockets can be a significant portion of the total project.

#### Standoffs

One simple way to mount an IC is to bend the leads radially outward and solder them to a grouping of eight or fourteen *Teflon*-insulated standoffs pressed into a glass-fiber or phenolic board. This method spreads the leads for easy wiring or testing, and it makes the IC easy to change. Fig. 1-15 shows this mounting technique. Both the standoffs and the IC's are easily reusable.

Fig. 1-15. IC mounted with insulated standoffs.

If the IC's are mounted right side up, the pin count will proceed counterclockwise, and the final wiring should correspond to the data-sheet numbering.

#### **Printed Circuit Boards**

IC's were designed for permanent insertion into printed circuit boards of the multilayer type. For simple circuits and digital instruments, singlesided PC boards with jumpers are an attractive alternate. Kits are available that permit making your own PC boards, using either the acid-resist or the photographic method.

Also, it is practical to use a "universal" PC master pattern with a grouping of IC land patterns that has only B+ and ground connected; connections can be made to the other terminals as necessary. These boards are commercially available and are reusable.

#### TOOLS

All of the conventional electronics hand tools carry over for IC work, although the smaller 4½-inch "jeweler's" diagonal cutting pliers and needlenose pliers are preferable to the larger "electronic" pliers. Several additional tools are necessary for IC work:

- 1. Syringe-type desoldering tool for removing IC's and correcting wiring errors.

- 2. Wire cleaner for desoldering tool.

- 3. Pocket magnifier for inspecting solder connections.

- 4. Knife for cutting circuit-board connections, separating solder bridges, and similar uses.

- 5. Toenail clipper for close cutting of soldered leads on printed circuit board.

- 6. Machinist's scriber for general probing.

- 7. Small vise or other way of holding circuit boards securely for close-in work.

- 8. Hand drill or miniature drill press. Most IC's require a No. 67 hole for each lead; larger components require a No. 60 hole. Drills of these small sizes cannot last long in a hand-held ¼-inch electric drill, even if the chuck will close down tightly enough to center them.

- 9. Pin vise and No. 67 drill for PC-hole cleaning and rework.

#### SOLDERING

Always use a small soldering iron rated at 40 watts or less and very fine solder when soldering IC's in place. While the IC's themselves can withstand any reasonable amount of heat, problems with solder bridging, foil lifting, and poor joints increase when larger irons are used. Soldering guns are awkward for this kind of work and should not be used. A temperaturecontrolling iron stand is a handy accessory if a great deal of IC work is to be done.

Be certain to double-check the IC connections before soldering. It is so easy to put the IC in upside down, to rotate it a lead or two, or worse yet, to put an IC in the wrong place.

To remove an IC, use a syringe-type desoldering tool, and carefully remove *all* the solder from each lead, one at a time. Then carefully pry up the IC. It should pop loose safely with no trouble at all.

#### POWER REQUIREMENTS

All the IC's of Fig. 1-14 are rated to operate from a 3.6-volt dc supply. In reality, most gate-only circuits will operate properly from a supply of 1.5 to 4.5 volts dc, and the more critical circuits using flip-flops will operate from a supply of 3.1 to 4.1 volts dc. This voltage is easily obtained from batteries or from a low-voltage, high-current line-operated supply.

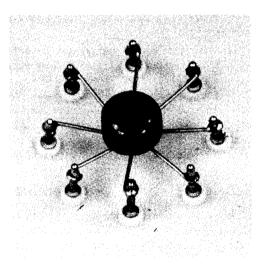

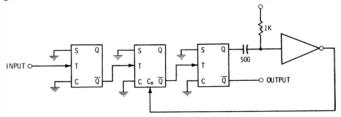

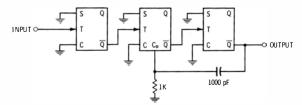

Whatever power source is used, it is absolutely essential that proper high-frequency bypassing be provided for the IC's. This bypassing may be accomplished by placing a  $0.1-\mu$ F and a  $100-\mu$ F capacitor in parallel at the IC end of the power-supply runs. The shortest possible leads should be used (Fig. 1-16). It is also important to use large leads (or wide foil runs) for both the B+ and ground connections to minimize noise effects.

The choice of batteries versus line operation depends on how many IC's are to be used, how portable the finished circuit must be, and whether the extra expense of a low-ripple power supply is justified. The first step in this decision is to calculate the current and power requirements.

Fig. 1-16. High-frequency bypassing of power leads.

#### CURRENT REQUIREMENTS

Table 1-1 shows the approximate average current drain for each logic block. To obtain the total current requirement, just add the currents for the individual elements. For instance, suppose we design a circuit that has three dual flip-flops, one dual buffer, and one dual two-input gate, all of which are medium-power RTL. The total current will be:

| 6 flip-flops at 2 | 22 mA         | 132 mA        |

|-------------------|---------------|---------------|

| 2 buffers at 42   | 84 m <b>A</b> |               |

| 2 gates at 6 mA   |               | 12 m <b>A</b> |

|                   | Total         | 228 mA        |

Thus, our supply would have to provide about 228 mA. To be on the safe side, we would design around a 250-mA supply. The total power requirement would be equal to the supply voltage multiplied by the supply current, or in this case 3.6 volts  $\times$  228 mA = 820 milliwatts, or, nominally, about one watt.

Note that a large number of flip-flops or buffers always means a large supply current. Thus the more complex IC circuits will be quite difficult to power with batteries.

#### BATTERY OPERATION

Ordinary flashlight cells, either two or three to the holder, may be used with many IC circuits, provided they are properly bypassed, and provided

| LOGIC BLOCK      | CURRENT (mA) |

|------------------|--------------|

| Medium-P         | ower RTL     |

| Inverter         | 6            |

| Gate             | 6            |

| Buffer           | 42           |

| JK Flip-Flop     | 22           |

| Expander         | 0            |

| Low-Pox          | wer RTL      |

| Gate             | 1            |

| Buffer           | 9            |

| JK Flip-Flop     | 6            |

| Type-D Flip-Flop | 6            |

Table 1-1. Current Requirements for Logic Blocks

\*With 3.6-volt dc supply (approximate values)

they can supply enough current for a long enough time. If the batteries are to last longer than about five hours, the maximum current drains listed in Table 1-2 should not be exceeded. Note that for circuits that take more than about 150 mA, the heavy-duty D cells or the more expensive alkaline cells must be used. For more details on battery life versus current drain, consult any of the handbooks published by many of the leading battery manufacturers.

Table 1-2. Maximum Current Drains

| Type of Cell                  | Current (mA) |

|-------------------------------|--------------|

| Flashlight "AA" (carbon-zinc) | 30           |

| Flashlight "C" (carbon-zinc)  | 90           |

| Flashlight "D" (carbon-zinc)  | 150          |

| Heavy-Duty "D" (carbon-zinc)  | 200          |

| Heavy-Duty "D" (alkaline)     | 300          |

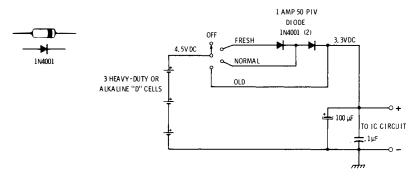

One way to extend the life of the larger cells is to add a two-diode "battery-saver" selector switch, as shown in Fig. 1-17. When the switch is in the FRESH position, the battery will measure 4.5 volts, and the two 0.6-volt forward drops of the silicon diodes will produce a 3.3-volt output. As the battery ages, the switch is changed first to the NORMAL position, and finally to the OLD position, retaining about 3.3 volts at the output, even with the cells discharged to 1.1 volts each. With this technique, battery life may easily be doubled.

Another, somewhat expensive, alternative is to use rechargeable nickelcadmium cells. Three 1.2-volt D cells nicely add up to 3.6 volts, and may be recharged many times. The 2000-mA-hr/200-mA-rate cell is suitable for many large projects.

Fig. 1-17. "Battery saver" circuit.

When indicator lamps are used with the IC's, their current requirements must also be taken into account. Dry-battery operation is usually impractical in any circuit with more than three indicator lamps in addition to the IC load.

#### LINE OPERATION

Ac-line operation requires immense electrolytic capacitors, a regulator, or both to obtain the low ripple at high current levels required for IC work. The elegance of the required supply increases with the current requirements and the complexity of the actual IC circuit.

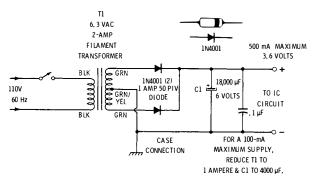

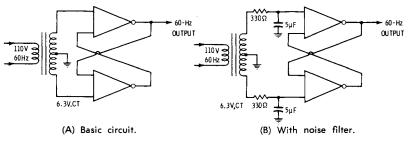

For a circuit using IC's only and no indicators, with a total current drain of less than 500 mA, the brute-force filtered supply of Fig. 1-18 may be used. The circuit includes a conventional filament transformer, two silicon diodes, and a large-value electrolytic capacitor. The immense capacitance is required in order to provide a low ripple at high current levels. Computer-grade electrolytic capacitors of this size are priced in the under-five-

Fig. 1-18. Filtered dc power supply.

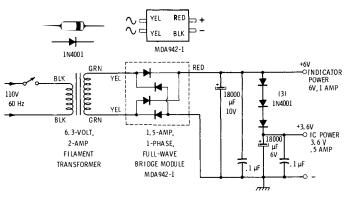

Fig. 1-19. Dual-voltage dc supply.

dollar range and measure about 11/2 inches in diameter by 5 inches long.

A two-voltage, brute-force filtered supply is shown in Fig. 1-19. Here, 3.6 volts dc at 500 mA or less and 6 volts at 1 ampere are provided. This type of supply is ideal for IC projects which include indicator lamps.

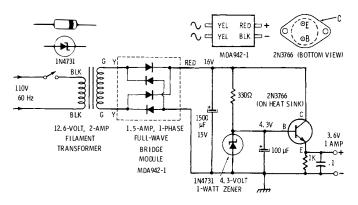

Fig. 1-20 shows a regulated supply that uses relatively small-value electrolytic capacitors and that will provide 3.6 volts at 1 ampere. For applications requiring higher current, this supply may be "beefed up" with larger rectifiers and filters, and a bigger power transistor.

Fig. 1-20. Regulated dc power supply.

#### "BAD" AND "BURNED OUT" INTEGRATED CIRCUITS

There are countless examples of IC work in which, if the circuit did not operate on the first try, the IC's were immediately blamed and considered "bad" or "burned out." In reality, RTL IC's are almost indestructible, and the likelihood of getting a defective new one is very slight. The IC's are neither heat nor static sensitive and will withstand considerably more than normal soldering heat. So long as circuit voltages are less than 5 volts or so, the IC will withstand virtually any combination of shorted or reversepolarity connections without failure.

The real gremlin is not a bad IC, but sloppy or careless workmanship solder bridges between connections, poor soldering, reverse supply polarity, a PC layout error, the wrong IC in the socket or the IC in upside down or rotated one pin, a PC board layout done bottom-view and the IC's inserted top-view (reversing all the connections), or the omission of high-frequency supply bypassing. These are the real problems in most IC circuits and account for practically all circuit problems. Be sure to watch for them.

## Logic and Switching Circuits

Digital-logic gates often are used as high-speed electronic switches. They also are used to respond to the coincidence or absence of input signals to follow a set of logic rules. In this chapter, the logic gate as a switch will be emphasized—how to use it, what rules to follow, and how to design any desired switching function with digital-logic gates.

#### THE TWO-INPUT GATE AS A SIMPLE SWITCH

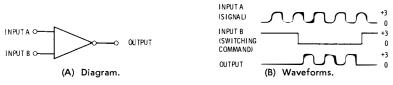

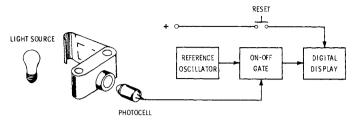

Suppose we wish to turn a train of pulses on and then turn them off again under command. For instance, we might like to allow high-frequency pulses to enter an electronic counter for precisely one second. The *readout* of the counter would then indicate the total number of pulses present during the second, or the frequency of the input in pulses per second. To do this, a two-input gate may be used as in Fig. 2-1.

So long as the switching waveform (input B) is positive, the output of the two-input gate will stay grounded. If terminal B is grounded, the two-input gate will respond to the signal waveform (input A), and an inverted replica of input A will appear at the output. Pulses will appear at the output *only* when input B is grounded. Thus the gate serves as a simple electronic switch.

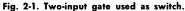

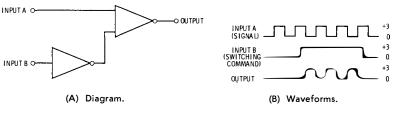

If we would rather control the switch with a positive-going waveform, we may simply add an inverter to input B. This circuit is shown in Fig. 2-2. Here, the input signals at A are passed and inverted only if terminal B is positive; the signals are blocked if terminal B is grounded. In Fig. 2-3, an inverter has been added to input A also. Now, pulses are passed "right side up" only when input B is positive.

This circuit could be built with a dual two-input gate and two inverters, or with a quad two-input gate by itself. If the one-package quad two-input

gate is used, two inputs are grounded to give the required two inverters, one gate is used "as is," and one is left over for use elsewhere.

This form of electronic switch is useful when it is desired to turn a digital signal on or off electronically, or when it is desired to *sample* a portion of a digital signal. RTL electronic switches may be operated at frequencies from dc to 10 MHz, and at speeds between 50 nanoseconds and many hours.

Fig. 2-2. Electronic switch for positive input.

There are some features of the simple electronic switches discussed so far that might not be desirable in some special applications. The switch may be turned on either just before or just after the instant a pulse arrives on input A. If we watch the switch output from sample to sample, we would obtain a roundoff error of plus and minus one count. In an electronic counter, this would make the last digit fluctuate. Also, the switch might be turned on *during* an input pulse; the output would then contain part of a pulse. If the time *width* of each pulse at input A is critical later on in the circuit, the switching will introduce a timing error. To get around these problems, it is necessary to resort to a *synchronized* electronic switch, a slightly more complex circuit described in Chapter 5.

Fig. 2-3. Noninverting electronic switch.

#### **COMPUTER LOGIC**

The rate at which signals appear at either input A or B has nothing to do with the switch operation. There could just as easily be a long gating waveform on terminal A and a series of short pulses on input B, or the pulses appearing at A and B could have nearly the same time duration.

In the latter case, the two-input gate responds to the coincidence or absence of the input pulses. For instance, if either input is made positive, the output goes to ground. If both inputs are grounded, the output goes positive. We say that the output goes positive on the *coincidence* of grounded input signals, and it goes to ground on the presence of either input positive. This type of circuit crops up over and over again in computers, and a whole set of rules, called *computer logic*, has been established to allow you to design any circuit you want that will respond to the presence or coincidence of inputs in any desired manner. We cannot change what the two-input RTL gate does—its output *always* goes positive on coincident grounded inputs, and always goes to ground with either input positive. What we can do is *interconnect* enough gates and inverters in a more complex circuit to get the desired result.

#### ONES AND ZEROS

So far, we are dealing only with digital input signals. A gate input must be either positive or grounded. In other words, any gate can have only one of two possible *states* on one of its inputs; similarly, at its output it can produce only one of two possible states. To identify these two possibilities, one state is called a *one* and the other a *zero*.

Now, we have a choice: Do we call the grounded state a zero and the positive state a one, or do we call the grounded state a one and the positive state a zero? It all depends. It is standard to assign the designation one to something we want and the designation zero to the absence of something we want. Rules and names for the rules are established only on what combination of ones at the inputs is required to get a desired output. Then, the definition of what a one is (grounded or positive) is chosen to "fit" the easiest possible way to make the circuit using RTL.

Logic functions are arranged according to what we want the ones to do. A suitable definition of a one is chosen to get the two-input RTL gates to give the desired results. Before we do this, however, it is necessary to take a closer look at the actual computer logic functions.

#### THE NOT CIRCUIT

A NOT gate is a one-input gate, or inverter. This circuit always automatically converts a one to a zero and vice versa, regardless of our definitions. This process is called *generating the complement*. Sometimes the more complex logic blocks have both an output and the complement of that output already available. If this is the case, the NOT circuit is already built in, and it is only necessary to pick the proper output to do the job.

People who work with computers have a way of building up a chart that illustrates how each logic function works. To do this, they simply list all possible combinations of inputs and then indicate for each combination the only permissible output that fits the logic function they are trying to generate. Such a chart for the NOT logic function is made up as follows: The

Fig. 2-4. Logic chart for NOT function.

chart is begun by listing all possible conditions on all possible inputs. With a NOT function, there is only one input, and it can only be a 1 or a 0 (Fig. 2-4A). The chart is completed by listing the outputs the NOT function produces: one produces a zero, and zero produces a one (Fig. 2-4B).

#### **TWO-INPUT LOGIC FUNCTIONS**

There are a number of two-input logic elements, each of which has a descriptive name. Just what each circuit does is most easily shown with the aid of charts similar to the one just developed for the NOT function.

#### **OR Circuit**

The OR circuit provides a 1 output if *either* input is a 1. The chart becomes a bit more complicated; now there are two inputs with two possible states on each input, giving four possible combinations. The chart for this logic function is shown in Fig. 2-5. This type of circuit is used whenever it is desired that *any* input produce an output.

#### NOR Circuit

NOR is shorthand for NOT OR. This circuit gives a 0 output if *either* input is a 1, and its chart looks like Fig. 2-6. The NOR circuit may be used any time it is necessary that *any* input *block* an output.

| INPUT A | INPUT B | OUTPUT |

|---------|---------|--------|

| 0       | 0       | 0      |

| 1       | 0       | 1      |

| 0       | 1       | 1      |

| 1       | 1       | 1      |

|         |         |        |

Fig. 2-5. Logic chart for OR function.

|                                         | INPUT A | INPUT B | OUTPUT |

|-----------------------------------------|---------|---------|--------|

| Fig. 2-6. Logic chart for NOR function. | 0       | 0       | 1      |

|                                         | 1       | 0       | 0      |

|                                         | 0       | 1       | 0      |

|                                         | 1       | 1       | 0      |

# **AND Circuit**

The AND logic function gives a 1 output only if both inputs are 1's (Fig. 2-7). This circuit is quite popular. It is used any time we want only the coincidence of input 1's to produce an output.

Fig. 2-7. Logic chart for AND function.

| INPUT B | OUTPUT           |

|---------|------------------|

| 0       | 0                |

| 0       | 0                |

| 1       | 0                |

| 1       | 1                |

|         | 0<br>0<br>1<br>1 |

# NAND Circuit

NAND is shorthand for NOT AND. This logic function gives a 0 output only if both inputs are 1's (Fig. 2-8). The NAND function blocks an output only when coincident 1's appear at its input.

| Fia  | 2-8          | Logic | chart  | for | NAND  | function. |

|------|--------------|-------|--------|-----|-------|-----------|

| FIG. | <b>Z-</b> 0. | LOGIC | Cilari | 101 | INAIN | ronchon.  |

| INPUT A | INPUT B | OUTPUT |

|---------|---------|--------|

| 0       | 0       | 1      |

| 1       | 0       | 1      |

| 0       | 1       | 1      |

| 1       | 1       | 0      |

|         |         |        |

# Half Adder (EXCLUSIVE OR) Circuit

The half adder, or EXCLUSIVE OR, logic function gives a 1 at the output if a 1 is present at either input, but not both (Fig. 2-9). What makes this logic function so useful is that it obeys the laws of binary (or base-two) addition. This provides the basic means for a computer to add two numbers together.

#### Fig. 2-9. Logic chart for EXCLUSIVE OR.

| INPUTA | INPUT B | OUTPUT |

|--------|---------|--------|

| 0      | 0       | 0      |

| 1      | 0       | 1      |

| 0      | 1       | 1      |

| 1      | 1       | 0      |

|        |         |        |

In the base-two number system, there are only two digits, 1 and 0. The binary addition rules are:

$$0 + 0 = 0$$

$1 + 0 = 1$

$0 + 1 = 1$

$1 + 1 = 0$  and carry 1

Just as in base-ten arithmetic, we add one column of two numbers together, and, if there is a carry, add it to the next column to the left. Thus, decimal 2 in the binary system is 0010; decimal 6 is 0110; and their sum is 1000, or decimal 8.

The reason that the EXCLUSIVE OR is called a half adder is that a carry may be left over from the previous column. A first half adder must add this possible carry to the first of the two numbers to be added; a second half adder must then add this *result* to the second number in each column. Two cascaded EXCLUSIVE OR circuits are called a *full adder*, and are the key to practically all computer calculations.

Once we have addition, we can add repeatedly to perform multiplication. If definitions are changed slightly to borrow instead of carry, we can subtract. And repeated subtraction is division. More complicated operations can be carried out easily by repeated sequential combinations of the basic addition-subtraction process.

# **Correlator, or EXCLUSIVE NOR**

The correlator circuit provides a 1 output if the inputs are identical, and a 0 output if the inputs are different (Fig. 2-10). The correlator logic function is used to *verify* that two binary numbers are identical, or to check to be sure that the same thing is happening at two different places in a circuit at the same time. This configuration is particularly handy for error detection and for electronic recognition, code, and coincidence circuits.

| INPUT A | INPUT B | OUTPUT |

|---------|---------|--------|

| 0       | 0       | 1      |

| 1       | 0       | 0      |

| 0       | 1       | 0      |

| 1       | 1       | 1      |

|         |         |        |

Fig. 2-10. Logic chart for EXCLUSIVE NOR.

# **Other Two-Input Logic Functions**

There are 16 possible two-input logic functions if a function is designed arbitrarily to fit every possible combination of 1's and 0's on the two-input chart. Six have just been discussed. The remaining ten functions are either worthless or so specialized that they would rarely, if ever, be used.

# MULTIPLE-INPUT LOGIC

There are 256 possible logic functions with a three-input gate, 65,536 with a four-input gate, and so on. Generally speaking, the six functions

already talked about for the two-input gate are often the only ones that are needed or that are really useful.

The rules carry over directly. On a three-input gate the OR function provides a 1 at the output for a 1 at any input; the AND function must have a 1 at each and every input to produce a 1 at the output, and so on.

# **BUILDING LOGIC FUNCTIONS WITH RTL**

How do we actually *build* these logic circuits using RTL integrated gates? Remember, the only thing an RTL gate can do is provide a grounded output when any input is positive, and a positive output only if all inputs are grounded. The first step is to decide what a 1 is to be.

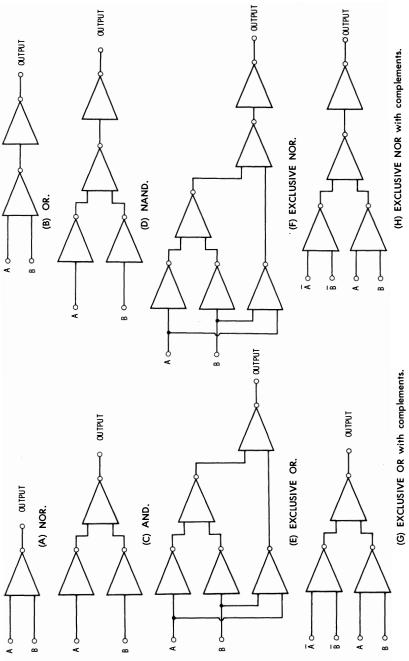

Suppose our definition says a 1 is the grounded state. The six two-input logic circuits are built as shown in Fig. 2-11. Here, the single two-input gate serves directly as a NAND circuit (Fig. 2-11A), for both inputs must have 1's (be grounded) for there to be a 0 (+) output. For an AND circuit (Fig. 2-11B), the output is inverted with a NOT gate. Both inputs are inverted to get an OR gate (Fig. 2-11C), and both inputs and the output are inverted to get a NOR gate (Fig. 2-11D).

The EXCLUSIVE NOR circuit (Fig. 2-11E) combines an OR circuit with a NAND circuit. The OR circuit works normally unless simultaneous 1's appear at the input. If this happens, the NAND circuit takes over and *inhibits*, or blocks, the inverting gate at the OR output. The EXCLUSIVE OR circuit (Fig. 2-11F) simply contains another inverter on the end of an EXCLUSIVE NOR.

Sometimes both the complement and the actual input signal are available. If this is the case, the last two circuits may be simplified as shown in Figs. 2-11G and 2-11H, nicely eliminating two inverters from the circuit.

Remember, all the circuits of Fig. 2-11 are good only if 1 is defined as ground and 0 is defined as +. Suppose we do the opposite. The gates all have to be changed around if 1 is defined as + and a 0 is defined as ground. For this *new definition*, the logic circuits are built up as shown in Fig. 2-12. Now the two-input gate by itself is a NOR gate (Fig. 2-12A). Invert the output for an OR gate (Fig. 2-12B), and both inputs for an AND gate (Fig. 2-12C). Invert the inputs and the output for the NAND (Fig. 2-12D).

The EXCLUSIVE OR (Fig. 2-12E) combines a NOR with an AND and an inhibiting inverter. A final inversion produces the EXCLUSIVE NOR (Fig. 2-12F). And once again, if inputs and their complements are readily available, two inverters may be saved, as shown in Figs. 2-12G and 2-12H.

#### CHOOSING LOGIC DEFINITIONS

There are special names for the "what-a-one-is" definitions. If a 1 is grounded, we are using *negative* logic; if a 1 is positive, we are using *positive* logic.

Fig. 2-12. Positive logic functions with RTL.

39

It appears there are two ways to realize any of the six basic logic functions. We can use negative logic, call a 1 the grounded state, and use the circuits of Fig. 2-11; or we can call a 1 positive, use positive logic, and use the circuits of Fig. 2-12. But which one do we choose? We pick the circuit that requires the fewest parts. If an entire system requires ten NAND gates, only ten two-input gates are needed with negative logic, but forty gates are needed with positive logic.

All of the gates in RTL are basically inverters, so when RTL is used the NAND and NOR circuits are always easier to build and require fewer parts. So, we usually bend our thinking to "fit" what RTL "likes" to do, and avoid the AND and OR functions wherever possible. In fact, it happens that practically everything done with RTL can be centered around the negative logic definition and the basic NAND gate. Later, it will be shown that the operation of counting flip-flops is *defined* only in terms of negative logic.

The choice of a logic definition boils down to this: Always use the negative logic definition *unless* you are absolutely certain that parts can be saved by using the positive logic definition. If there are any flip-flops at all in the circuit, you are likely to be forced into using the negative-logic circuits in any event. Above all, learn to think out RTL in negative logic—it is the logic you will use over 90% of the time. If a "1" being ground seems bothersome, try thinking of it as a saturated output transistor.

# WHAT GOOD IS LOGIC?

We now have all the rules for the two-input logic functions, and a choice of ways to build each circuit. What good is all this? Plenty.

Look again at the simple switch of Fig. 2-1; it is really a NAND gate. As will be shown in the next chapter, when two NAND gates are connected back-to-back, they acquire such features as memory, time delay, or pulse shaping, or they may serve as oscillators.

We have already seen how the EXCLUSIVE OR circuit directly performs binary arithmetic and forms the basis of all digital computer calculations. Also, it is possible to use NAND gates to make a binary counting chain count by any desired number, through a feedback process. More NAND gates can be used to *decode* the same counter, and produce a unique output for each and every counter state.

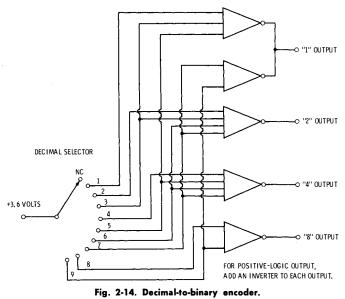

#### DECIMAL-TO-BINARY ENCODER

Gates may be used to convert from one number system to another, or to convert one code to another. Everyday arithmetic is done in base 10; computers work in base 2, coded in any of several dozen possible ways. Gates make it possible to convert decimal numbers to binary numbers, convert binary numbers to decimal numbers, and convert the various binary codes to each other.

| DECIMAL | BINARY<br>(8421) |

|---------|------------------|

| 0       | 0000             |

| 1       | 0001             |

| 2       | 0010             |

| 3       | 0011             |

| 4       | 0100             |

| 5       | 0101             |

| 6       | 0110             |

| 7       | 0111             |

| 8       | 1000             |

| 9       | 1001             |

Fig. 2-13. Decimal-binary equivalents.

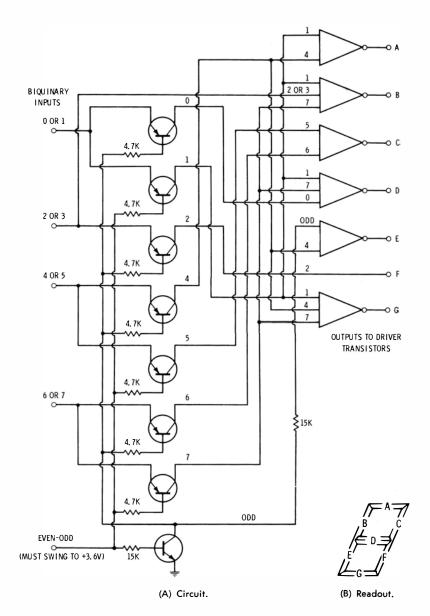

One popular binary code is called the *binary-coded decimal*, or 1-2-4-8, code. In this code, a decimal number corresponds to its binary equivalent up to count nine (Fig. 2-13). Each decimal decade is treated as a new binary number; when ten is reached, the conversion is repeated, one column to the left. Thus  $24 = 0010\ 0100$ ;  $395 = 0011\ 1001\ 0101$ , and so on. The binary equivalents 10 through 15 are not used; these are simply "thrown away."

This decimal-like grouping of binary numbers makes decimal-to-binary conversion easy, particularly for larger numbers. While this is a rather popular binary code, there are many others.

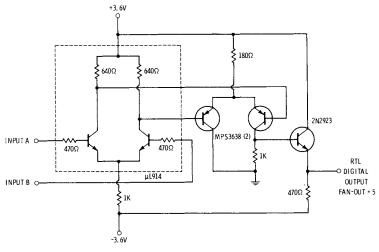

The process of going from decimal to binary numbers is called *encoding*, and an RTL decimal-to-binary encoder is shown in Fig. 2-14. A ten-position selector switch sets up the proper gates to produce the binary equivalent of the selected decimal number. Each gate is basically a NOR gate. As

Fig. 2-15. Binary-to-decimal decoder.

the selected gates receive base current, their outputs go to ground, producing negative-logic 1's at the output. If positive-logic 1's are desired, the outputs are simply inverted.

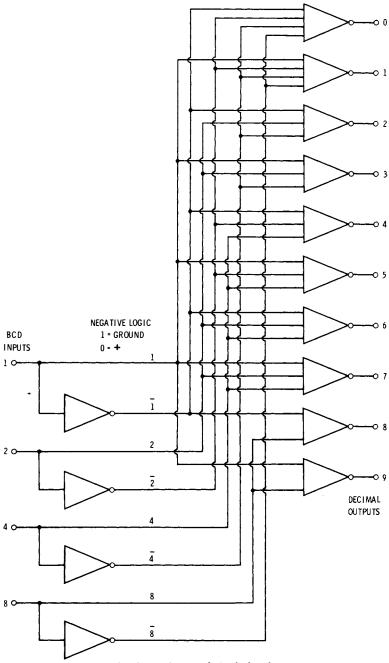

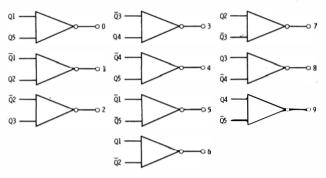

# **BINARY-TO-DECIMAL DECODER**

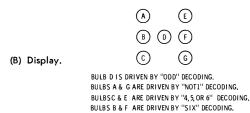

The opposite of encoding is called *decoding*. As Fig. 2-15 shows, ten gates are necessary to accept the 1-2-4-8 inputs, NAND them together, and produce the equivalent decimal output. A positive output voltage appears at the correct decimal output. This voltage then may be used to drive a lamp, a printer hammer, or something else in the outside world. If both the binary input and its complement are available, the four input inverters can be omitted.

Remember, the circuits in Figs. 2-14 and 2-15 are useful only for converting decimal to binary-coded-decimal, or 1-2-4-8, coding, and vice versa. There are many other binary codes (some will be covered later), and all the other codes require different encoding and decoding.

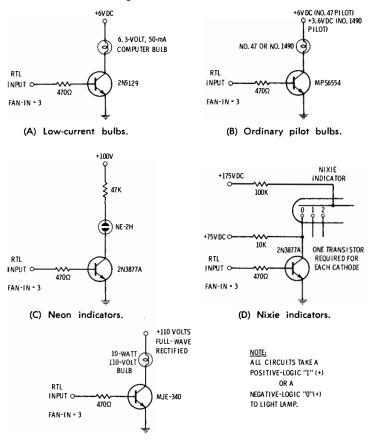

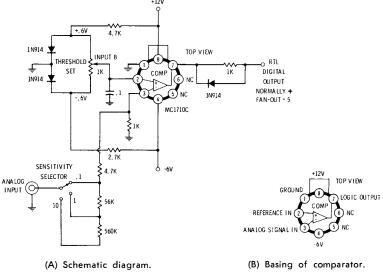

# INDICATING STATES: DRIVING THE OUTSIDE WORLD WITH RTL

Although a low-current, low-voltage light bulb can be operated directly from the output of an inverter, gate, or buffer, the brightness will be very low and the results highly nonuniform. There are several good ways to determine what state any RTL logic block is in, and several ways to transfer this information to the outside world. We can use a voltmeter, any lamp with a proper choice of drive transistor or SCR, a relay, printer hammer, or indicator coil, or an audio-tone module.

# Voltmeters

An ordinary VOM, a VTVM, or a transistor voltmeter can be used to check the output and input levels on any gate. The grounded state measures 0.2 volt or less. The positive-state voltage depends on the loading and the supply voltage; it will vary from 1.3 to 3.6 volts from a 3.6-volt supply. Just set the VOM to the 3-volt scale. If the pointer barely moves, the output is in the grounded state; if the pointer swings well up scale, the output is in the + state.

#### **Indicator Lamps**

Either transistors or SCR's can be used as lamp drivers. Npn *silicon* transistors are the best choice—their levels are immediately compatible with RTL, and they need the same supply polarity. Because saturated transistors have a very low input impedance, always add a series base resistor to any lamp driver, unless it is the only load presented to a gate. If you always make this resistor 470 ohms, you can be assured of at least 1 milli-

ampere of base-current drive, and an equivalent RTL fan-out requirement of approximately 3. Then select an npn transistor with enough gain and enough breakdown voltage to handle the lamp to be driven.

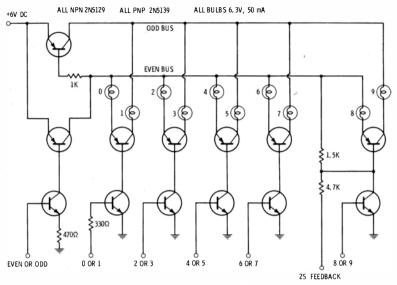

If low-current bulbs are used, they typically require 50 milliamperes of drive; to insure saturation, the drive transistor should have a gain of at least 50 at the 50-milliampere level. The 2N5129 transistor is suitable

(E) 110-volt lamps.

Fig. 2-16. Transistor lamp drivers.

and may be used to drive lamps requiring up to 28 volts. The circuit is shown in Fig. 2-16A.

The bulbs may be driven from dc, full-wave rectified dc, or half-wave rectified dc. With half-wave rectified dc, use double the normal bulb voltage. This will make the brightness the same for any type of supply. If there are many bulbs in the IC system, avoid using filtered dc on them, since it only adds expensive electrolytic capacitors to the circuit and makes the ripple worse for the rest of the circuit.

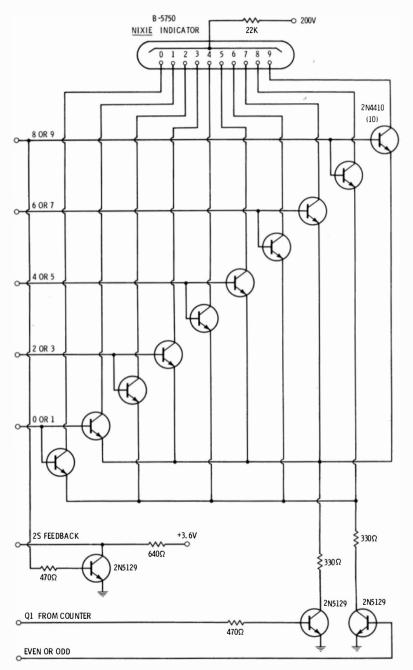

Ordinary pilot lamps need more current, so a transistor with a high gain at the 150-milliampere current level is needed. The MPS6554 may be used; the circuit is shown in Fig. 2-16B.

*Nixie* indicators, neon bulbs, and other numerical readouts require little current, but a high-voltage transistor is needed, as the circuits of Figs. 2-16C and 2-16D show. Two suitable transistors are the 80-volt 2N3877A and the 120-volt 2N4410. You can directly drive a 10-watt, 100-volt light bulb by using a 200-volt, high-gain power transistor. One transistor to use is the MJE-340, in the circuit of Fig. 2-16E.

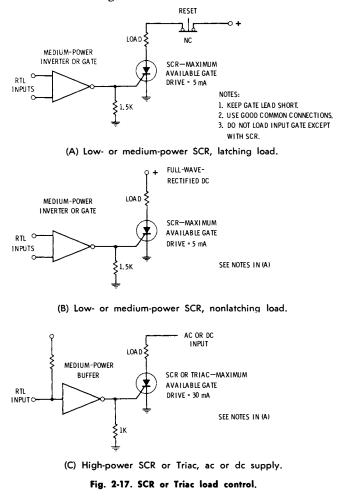

SCR's may be used to drive outside-world loads, as the circuits in Fig. 2-17 show. Ordinary low-current SCR's may be driven directly from an inverter or a gate, but the high-power *Triacs* and SCR's must be driven from a buffer. By using these high-power semiconductors, you can directly control several kilowatts of power with RTL. If an SCR or *Triac* is dc powered, it will latch on until it is reset manually. If these devices are powered from full-wave rectified dc, half-wave rectified dc, or ac, they will

automatically shut off shortly after the input signal does. Be sure to keep the gate-lead lengths very short and use good grounds and common connections to prevent any noise or interaction problems; in particular, prevent the SCR load current from affecting the RTL ground. This is particularly true of the new low-cost, plastic SCR's with their extremely sensitive gates.

More complex RTL circuits will allow proportional control of acpowered semiconductor switching devices without the use of trigger diodes and the usual phase-control circuitry. These techniques are most useful when zero-point switching, feedback, or dc voltage control is essential.

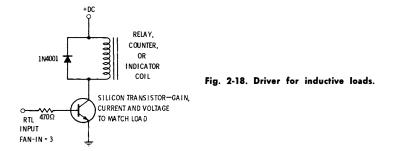

#### **Relays and Driver Coils**

Fig. 2-18 shows the techniques for driving inductive loads. The problems are the same as in driving lamps; pick a transistor with enough gain, current, and breakdown voltage to handle the load. When driving coils, be sure to add a damper diode as shown in Fig. 2-18; this protects the trans

Fig. 2-19. IC "logic-state checker."

sistor or SCR from a voltage spike if the semiconductor is turned off suddenly. If SCR's are used to drive relays, make sure the gate signal is present long enough to give the SCR a chance to turn on fully. Several milliseconds are usually adequate.

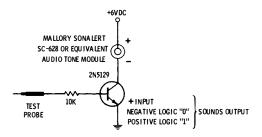

# **Audio-Tone Modules**

Some types of audio-tone modules may be directly driven with almost any npn silicon transistor in the circuit of Fig. 2-19. This arrangement provides an audio tone output, and serves as a useful "state-checker" for use in troubleshooting IC circuits.

# CHAPTER 3

# **Multivibrators**

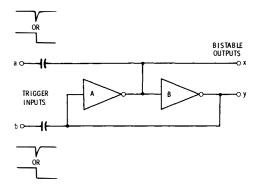

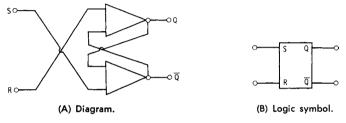

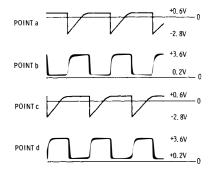

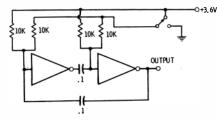

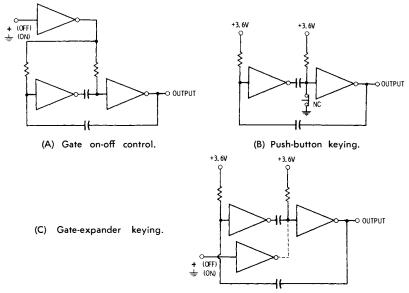

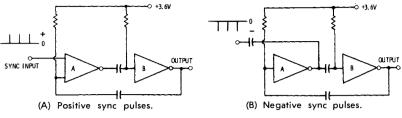

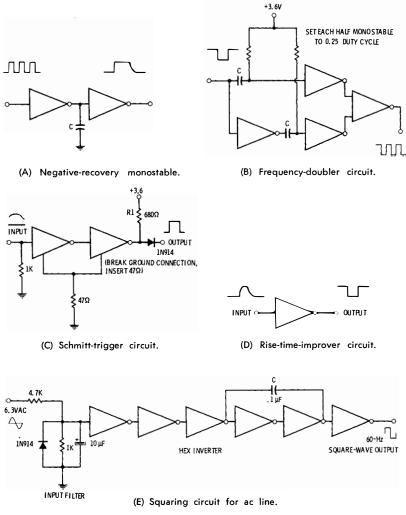

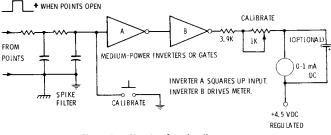

When two inverting gates are connected back-to-back, a *multivibrator* is formed. Depending on the connections, the multivibrator may have zero, one, or two stable states. Multivibrators are used for oscillators, memories, latches, pulse shapers, frequency multipliers and dividers, reset generators, time delays, signal conditioners, synchronizers, and level detectors. In this chapter, we will take a closer look at this back-to-back gate connection and see how to design any desired type of RTL multivibrator.

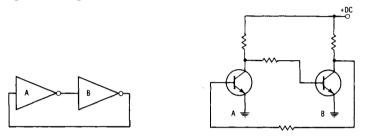

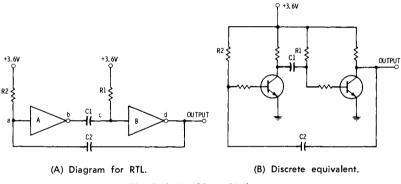

# TWO INVERTERS BACK-TO-BACK

Suppose, as in Fig. 3-1, we connect two inverters back-to-back so that the output of one inverter drives the input of the other inverter, and vice versa. The circuit has two stable states. If inverter A happens to be receiving no base current, it stays off. If inverter A is off, its output is positive and, in turn, delivers base current to inverter B. Therefore, inverter B will be on. If inverter B is on, its output is grounded; this condition is just what inverter A needs to stay off. If undisturbed, the two inverters will remain this way indefinitely.

We could just as easily have inverter B off and inverter A on; this state is just as stable. The circuit can be in one of two possible states; if undisturbed it will remain in either state. This action is somewhat similar to the latching of a mechanical relay on its own "make" contact.

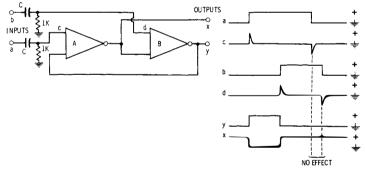

# TRIGGERING: THE BISTABLE MULTIVIBRATOR

The circuit in Fig. 3-1 would be far more useful if it could be forced to go into a desired one of the two possible states on command. The process of forcing the two back-to-back inverters into a desired state is called *trig*- gering; a triggerable pair of back-to-back inverters is called a *bistable mul*tivibrator (often shortened to "bistable").

Suppose, once again, that inverter A is off, and its output is shorted to ground momentarily. This removes base current from inverter B and turns B off. The output of B swings positive and provides base current for A; A turns on. When the momentary short is removed, A stays on. By shorting the output of inverter A, we have forced the bistable multivibrator to go into the state with the output of inverter A grounded and the output of inverter B positive. If the output of inverter B is shorted momentarily, the circuit will flip back to the state in which the output of B is grounded and the output of A is positive.

(A) Logic-symbol diagram. (B) Discrete equivalent.

Fig. 3-1. Inverters back-to-back.

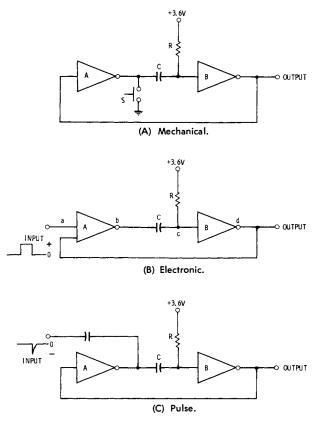

There are three ways to trigger a bistable multivibrator and force it to go into a desired state. It can be triggered mechanically with a contact or a switch, electronically with another gate input, or by capacitor coupling a negative pulse into the output of the off inverter.

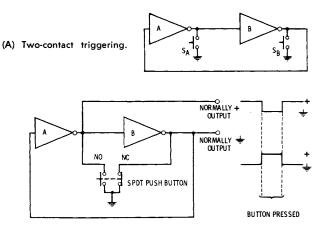

# **Mechanical Triggering**

In Fig. 3-2A, momentarily closing contact  $S_A$  grounds the output of inverter A. Momentarily closing contact  $S_B$  grounds the output of inverter B. Either contact closure forces the flip-flop to assume and *stay in* the desired state.

One major application of this simple circuit is to make a push button bounceless. Ordinary push buttons generate noise and contact bounce both on contact closure and on opening. If this noisy operation is fed directly to any high-speed IC circuitry, very erratic multiple counting and triggering is almost a certainty. To get around this problem, the circuit of Fig. 3-2B may be used with a spdt push button. Whenever the button is pressed, the normally open contact momentarily "makes," bounces for a while, and then finally comes to rest. The very first momentary closure triggers the bistable into one state; it remains in that state throughout the bouncing and settling time. When the button is released, the very first closure of the normally closed contact triggers the bistable back into its initial state. The result is a high-speed square wave, lasting from initial make to final release, that is bounce and noise free—and that has rise and fall times fast enough to drive reliably the fancier counting flip-flops to be discussed later.

Other possible applications of the mechanically triggered bistable are in latches and memory circuits. This circuit could be used in an annunciator or an alarm, or perhaps as the memory of a tick-tack-toe computer, reflex tester, or some other electronic game.

Fig. 3-2. Mechanical triggering of bistable multivibrator.

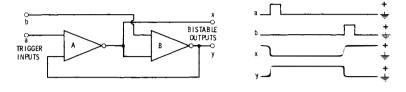

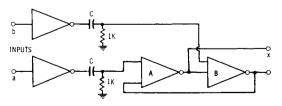

# **Electronic Triggering**

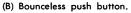

Instead of a one-input gate, Fig. 3-3A shows a two-input gate on each side of the bistable, and the outputs are cross-coupled to the inputs so that only one input is used on each gate. This connection leaves one input available on each side. When one of these inputs is made positive, the bistable flips into the state that grounds the output of the side whose input was made positive. Fig. 3-3B shows how narrow pulses are delivered to the desired input anytime it is desired to trigger the bistable. These pulses may be obtained from previous RTL circuits in the system. The first pulse must end before the second one arrives.

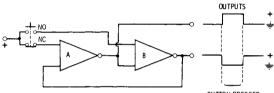

Fig. 3-3C shows another bounceless push button. This time, the contacts are used to deliver base current to the input of the desired gate. The only advantage of this circuit over the previous one is that you can buy a dual two-input gate, but inverters normally come six to a package. You can mount the dual two-input gate directly on the push button if you like, to make a bounceless button in practically the same space required by an ordinary one.

A leading-edge-sensitive bistable is shown in Fig. 3-3D. Here, if input a suddenly goes positive and stays positive, a brief triggering pulse is delivered to the bistable. This pulse is obtained by capacitor-resistor differentiation of the leading edge of the input signal. The same thing happens if input b suddenly goes positive. The bistable is now sensitive only to the *start* of the input signals, and not to their *duration*. The trailing edge, or end, of each input pulse has no effect since it delivers a *negative* turn-off pulse to an input that is already off.

(A) Method of triggering bistable.

(B) Triggered-multivibrator waveforms.

BUTTON PRESSED

(C) Circuit for bounceless push button.

(D) Leading-edge-sensitive triggering.

(E) Trailing-edge-sensitive triggering.

Fig. 3-3. Electronic triggering of bistable multivibrator.

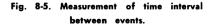

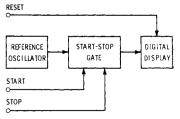

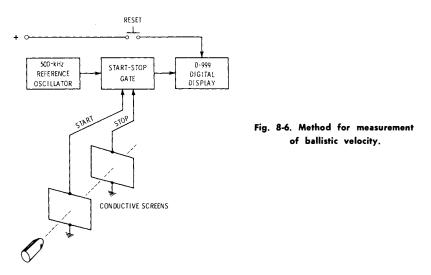

A use of electronic triggering would be in a ballistic chronometer. Two normally conductive screens are placed a known distance apart in front of a rifle. The bullet breaks the screens in sequence, causing the bistable to flip to one state the instant the bullet crosses the first screen, and flip back the instant the bullet crosses the second screen. The bistable output is used to turn on a reference-frequency source, the output pulses of which are counted. The counter output then indicates the time the bullet took to traverse the known distance between the two screens. When the time and distance are known, a simple division gives the velocity of the bullet.

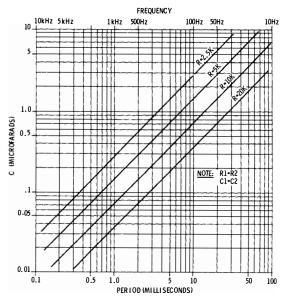

The choice of resistor and capacitor values depends highly on the circuit. The RC time constant has to be long enough to pass the rise of the input signal, but not so long as to interfere with the later change of state caused by the other input. A resistance of 1k is usually a good value for this circuit. With a 1k resistor, the capacitance in microfarads is equal to the time constant in milliseconds. With normal, high-speed RTL transitions, a good value for C is often 0.001 microfarad (1000 pF), with a resultant 1.0-microsecond time constant. Slower events, such as the breaking of the screens by the bullet, may require correspondingly longer time constants.

A trailing-edge-sensitive bistable (Fig. 3-3E) is obtained simply by inverting both inputs before differentiation. Now the leading edge has no effect, and the trailing edge produces a positive trigger pulse that flips the bistable into the desired state.

# **Pulse Triggering**

In Fig. 3-4, a negative turn-off pulse is coupled into the output of the off inverter. The negative pulse robs the on inverter of its base current long enough to allow the bistable to flip into its proper state. This triggering requires careful control of pulse amplitude and shape. It also depends on the output loading of the bistable, and a portion of the trigger amplitude may appear in the output.

Fig. 3-4. Pulse triggering of bistable multivibrator.

While this connection was quite popular with discrete transistor multivibrators, there is seldom, if ever, any need for it with RTL integrated circuits. Sometimes, however, if you need a sequence of cascaded time delays, this triggering mode may be of value.

#### LOADING

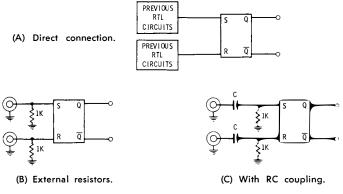

There are no loading restrictions on the bistable multivibrators except those of the gates or inverters themselves. In the case of a bistable built with medium-power RTL, the total fan-out per output is 16, of which 3 is needed to run the other input. This leaves 13 units of fan-out for outside use. A low-power gate starts with a fan-out of 4; 1 unit is needed to run the other gate, and an output fan-out of 3 remains. Fig. 3-5 shows the details. Two buffers may be used as a bistable, but unless an exceptional amount of fan-out is needed, the supply-power consumption favors the use of lower-power devices.

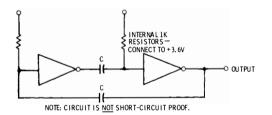

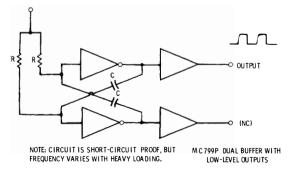

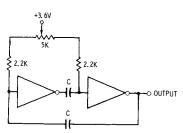

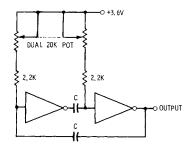

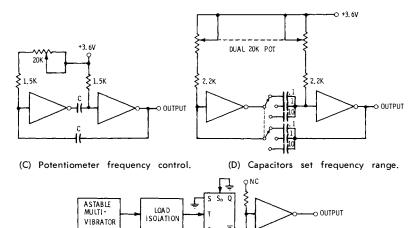

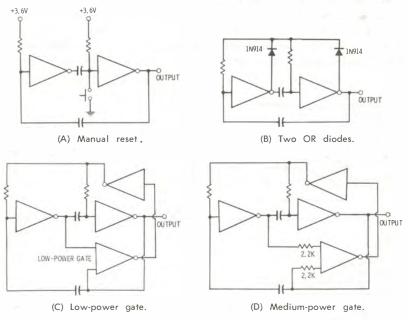

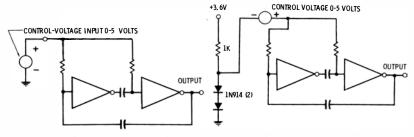

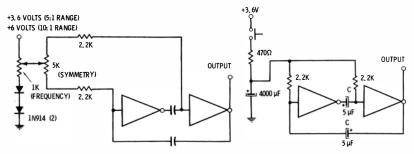

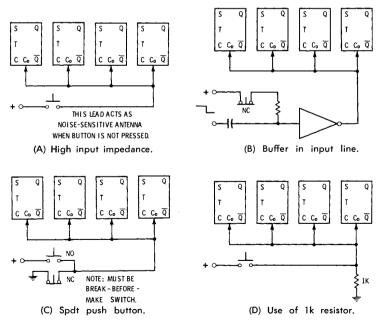

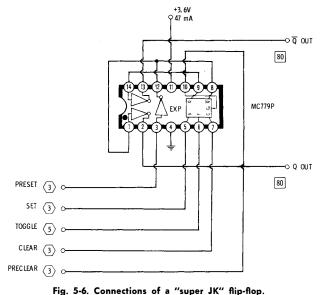

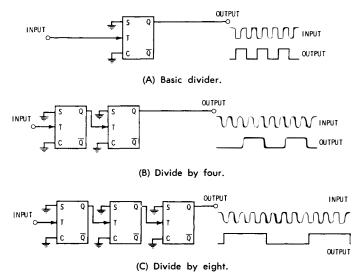

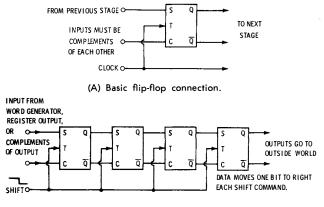

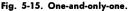

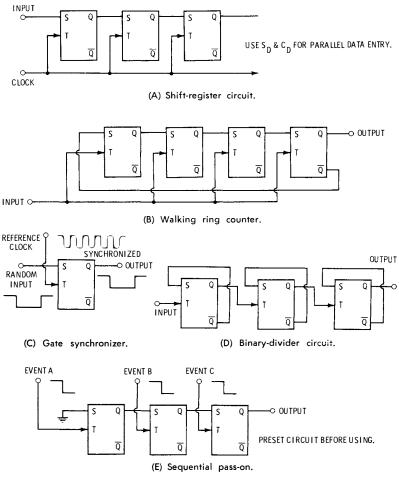

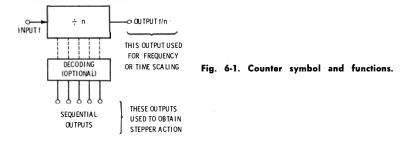

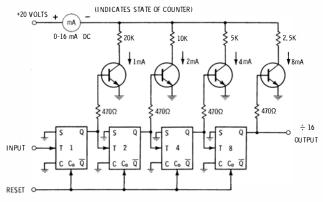

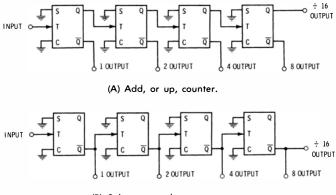

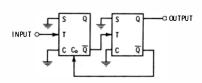

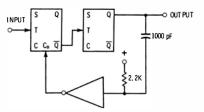

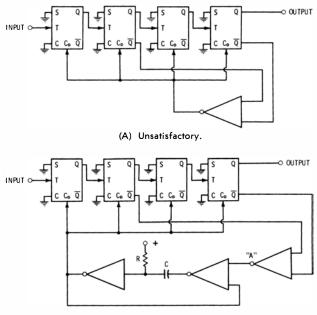

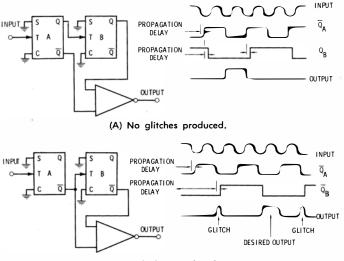

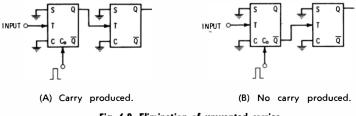

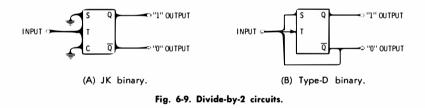

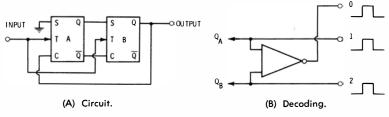

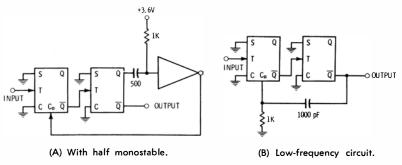

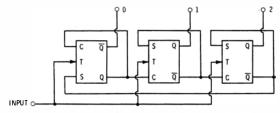

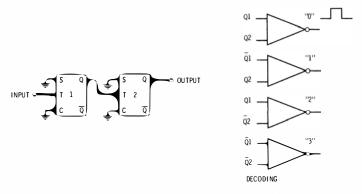

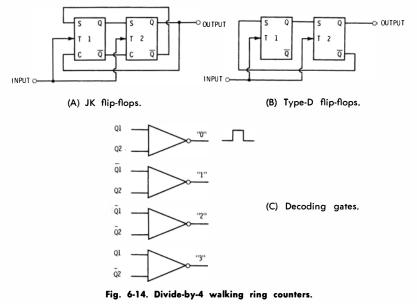

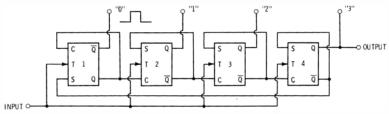

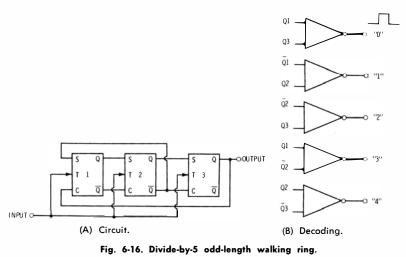

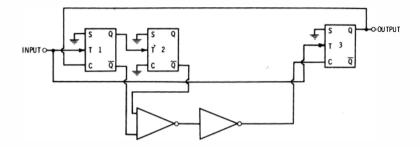

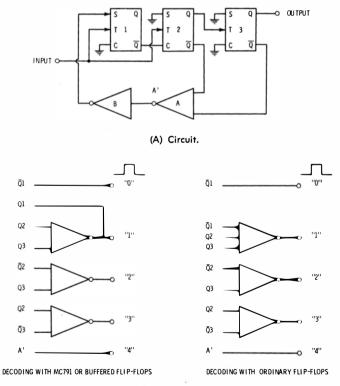

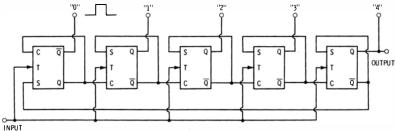

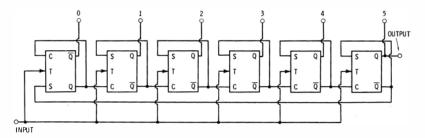

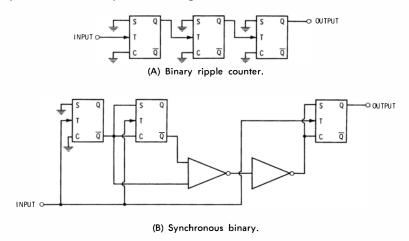

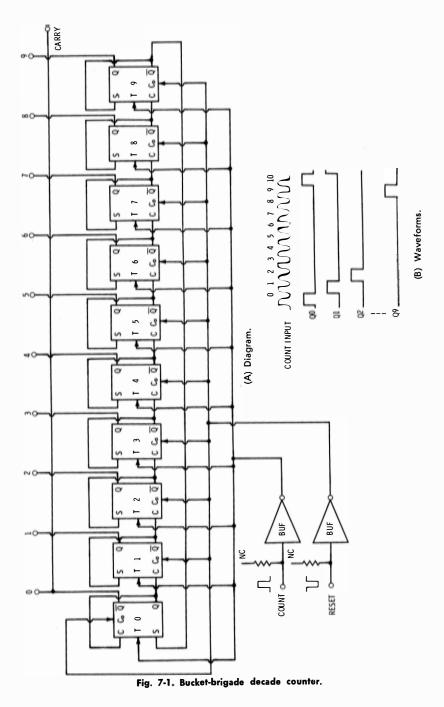

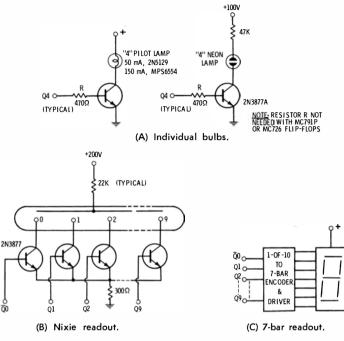

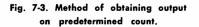

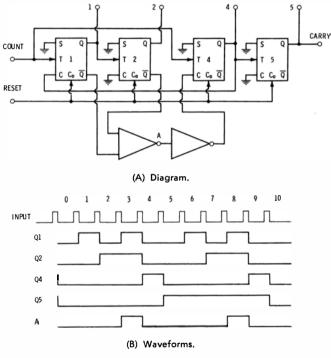

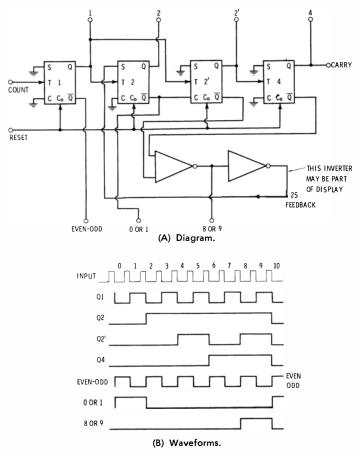

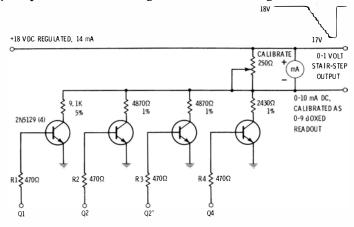

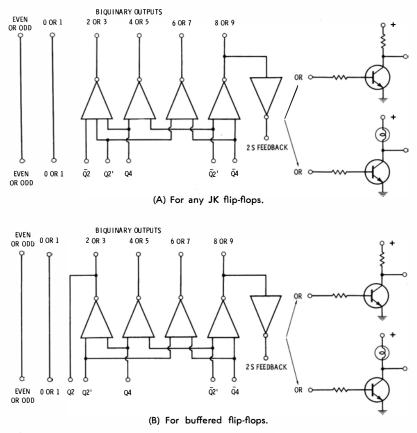

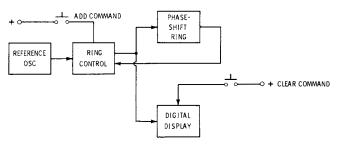

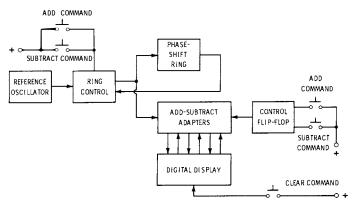

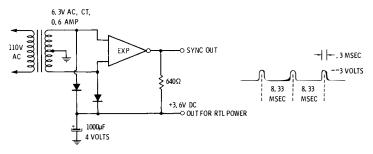

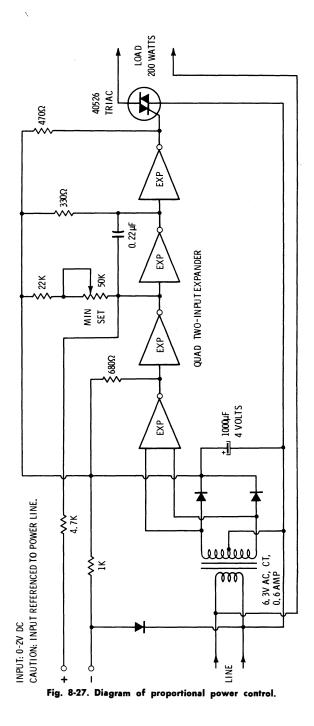

Fig. 3-5. Available output of a bistable multivibrator.